Controller area network (beCAN) RM0016

406/449 Doc ID 14587 Rev 8

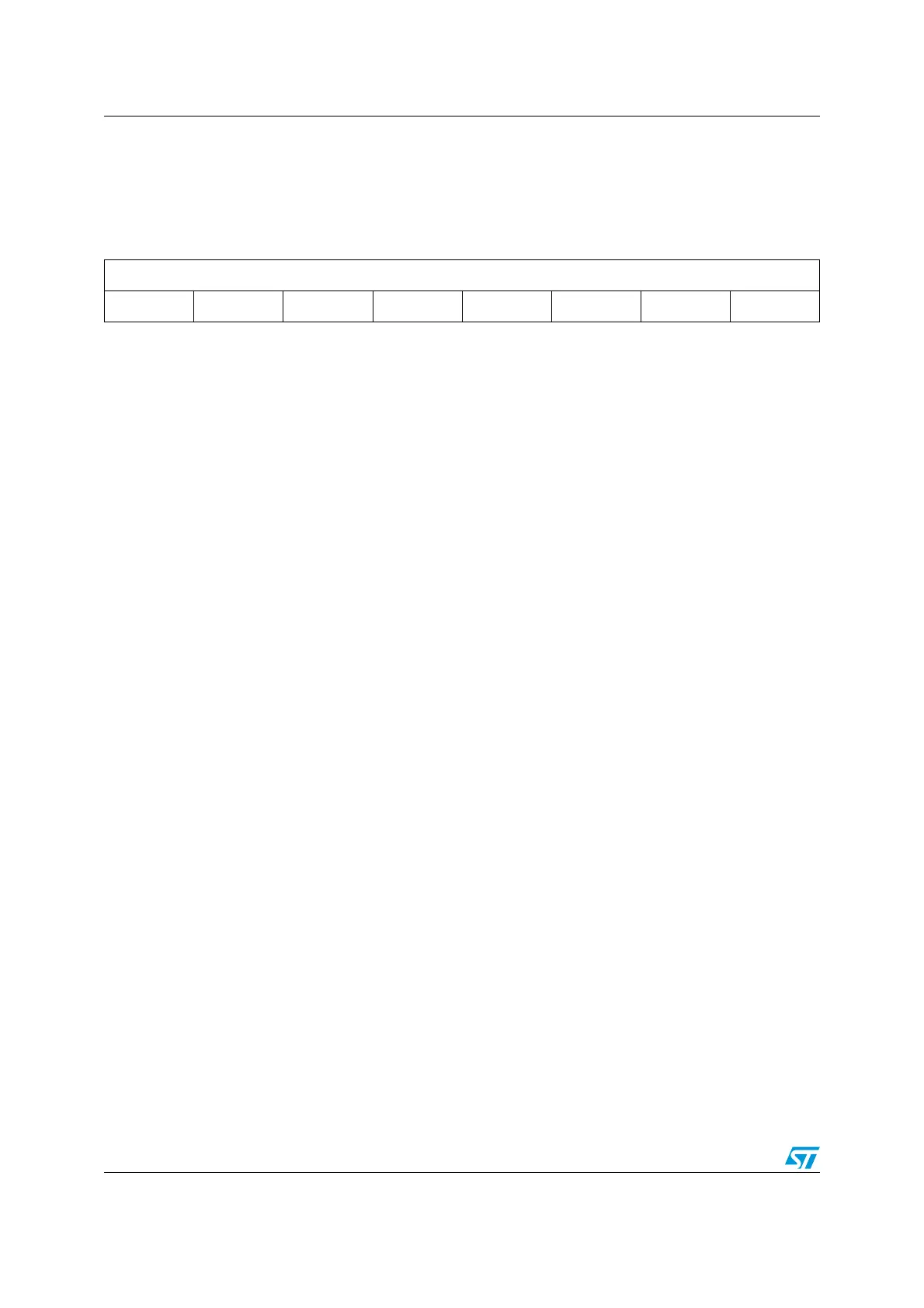

CAN filter bank i register x (CAN_FiRx) (i = 0 .. 5, x = 1 .. 8)

Address offset: See Figure 157.

Reset value: 0xXX

76543210

FB(7:0]

rw rw rw rw rw rw rw rw

Bits 7:0 FB[7:0]: Filter bits

– Identifier

Each bit of the register specifies the level of the corresponding bit of the expected identifier.

0: Dominant bit is expected

1: Recessive bit is expected

– Mask

Each bit of the register specifies whether the bit of the associated identifier register must match with

the corresponding bit of the expected identifier or not.

0: Don’t care, the bit is not used for the comparison

1: Must match, the bit of the incoming identifier must have the same level has specified in the

corresponding identifier register of the filter.

Note: Each filter i is composed of 8 registers, CAN_FiR1..8. Depending on the scale and mode

configuration of the filter the function of each register can differ. For the filter mapping, functions

description and mask registers association, refer to Section Figure 23.6.3: Identifier filtering.

A Mask/Identifier register in mask mode has the same bit mapping as in identifier list mode.

Note: To modify these registers, the corresponding FACT bit in the CAN_FCRx register must

be cleared.

Loading...

Loading...