LH79524/LH79525 User’s Guide Color Liquid Crystal Display Controller

Version 1.0 4-47

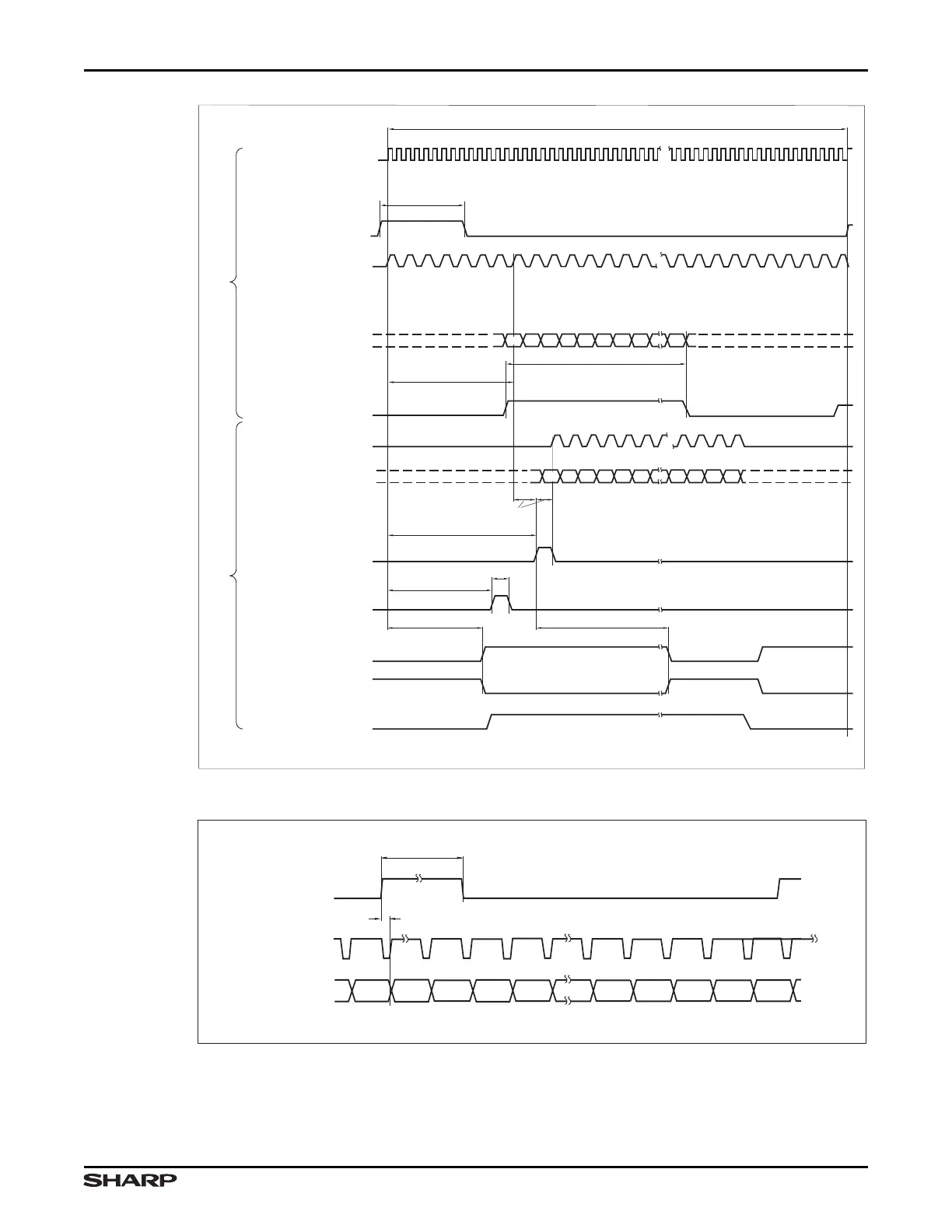

Figure 4-10. AD-TFT, HR-TFT Horizontal Timing Diagram

1 AD-TFT or HR-TFT HORIZONTAL LINE

AD-TFT and HR-TFT SIGNALS ARE TFT SIGNALS, RE-TIMED

TIMING0:HSW

TIMING0:HSW +

TIMING0: HBP

PIXEL DATA

1 LCDDCLK

002 003 004 005 006 318317 319 320001

1 LCDDCLK

ALITIMING1:LPDEL

ALITIMING1:PSCLS

ALITIMING2:PS2CLS2

ALITIMING2:SPLDEL

002 003 004 005 006 007 008 320001

*

CLCDCLK

(INTERNAL)

APBPERIPHCLKCTRL1:LCD

CLKPRESCALE:LCDPS

(SHOWN FOR REFERENCE)

LCDLP

(HORIZONTAL

SYNCHRONIZATION

PULSE)

INPUTS TO THE

ALI FROM THE CLCDC

OUTPUTS FROM THE

ALI TO THE PANEL

LCDDCLK

(PANEL CLOCK)

TIMING2:PCD

TIMING2:BCD

TIMING2:IPC

TIMING2:CPL

LCDVD[11:0] (LH79525)

LCDVD[15:0] (LH79524)

16 × (TIMING0:PPL+1)

LCDDCLK

(DELAYED FOR

AD-TFT, HR-TFT)

LCDVD[11:0] (LH79525)

LCDVD[15:0] (LH79524)

(DELAYED FOR

AD-TFT, HR-TFT)

LCDSPL

(AD-TFT, HR-TFT

START PULSE LEFT)

LCDLP

(HORIZONTAL

SYNCHRONIZATION

PULSE)

LCDCLS

LCDPS

LCDREV

LCDEN

(INTERNAL DATA ENABLE)

LH79525-42

NOTE: * Source is RCPC.

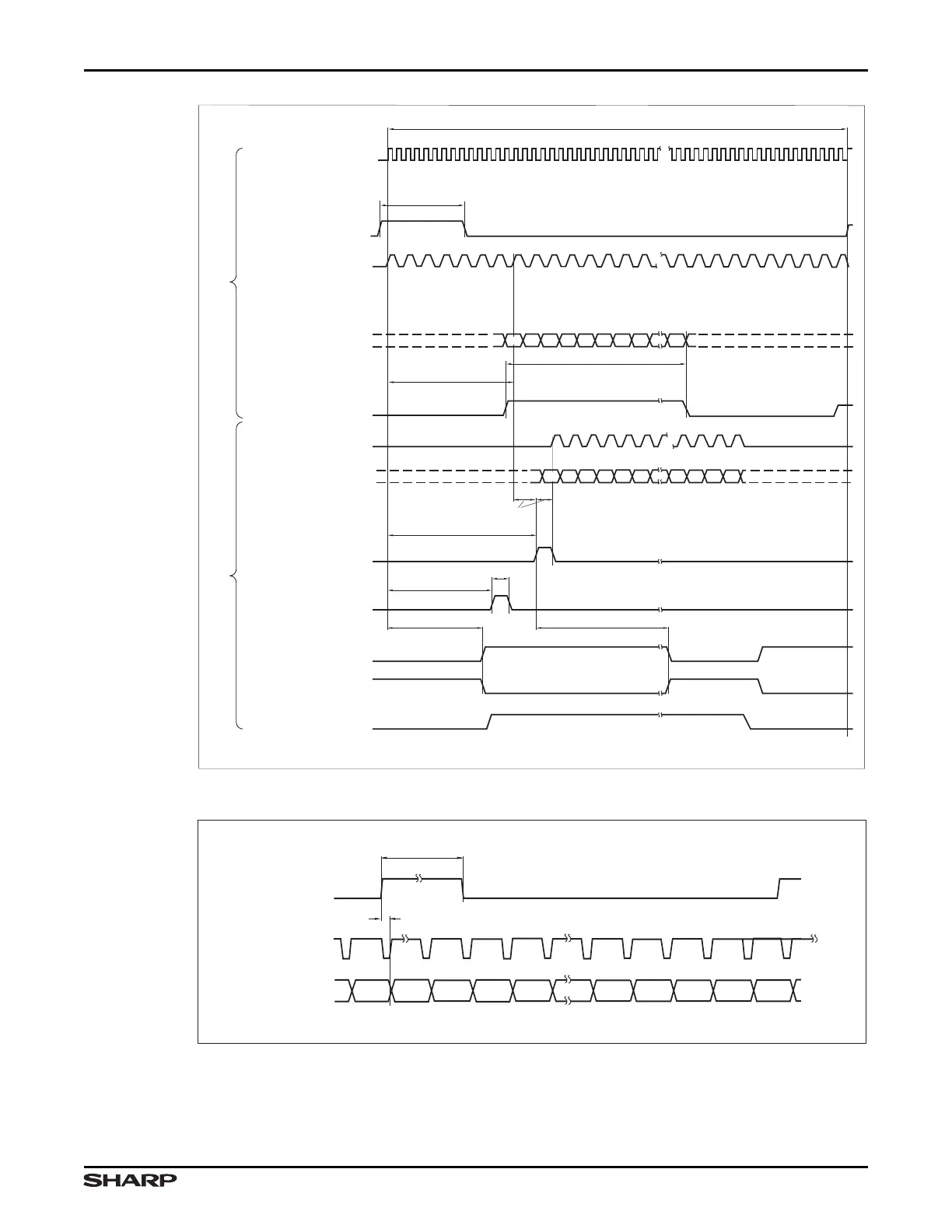

Figure 4-11. AD-TFT, HR-TFT Vertical Timing Diagram

LCDSPS

(VERTICAL

SYNCHRONIZATION)

LCDLP

(HORIZONTAL

SYNCHRONIZATION

PULSE)

LCDVD[11:0]

(LCD VIDEO DATA)

NOTE: LCDDCLK can range from 4.5 MHz to 6.8 MHz.

LH79525-4

TIMING1:VSW

1.5 µs - 4 µs

Loading...

Loading...