LH79524/LH79525 User’s Guide Ethernet MAC Controller

Version 1.0 6-29

6.3.2.7 Receive Status Register (RXSTATUS)

Read this register to obtain details of the status of a receive. Once read, individual bits may

be cleared by writing 1 to them. It is not possible to set a bit to 1 by writing to the register

.

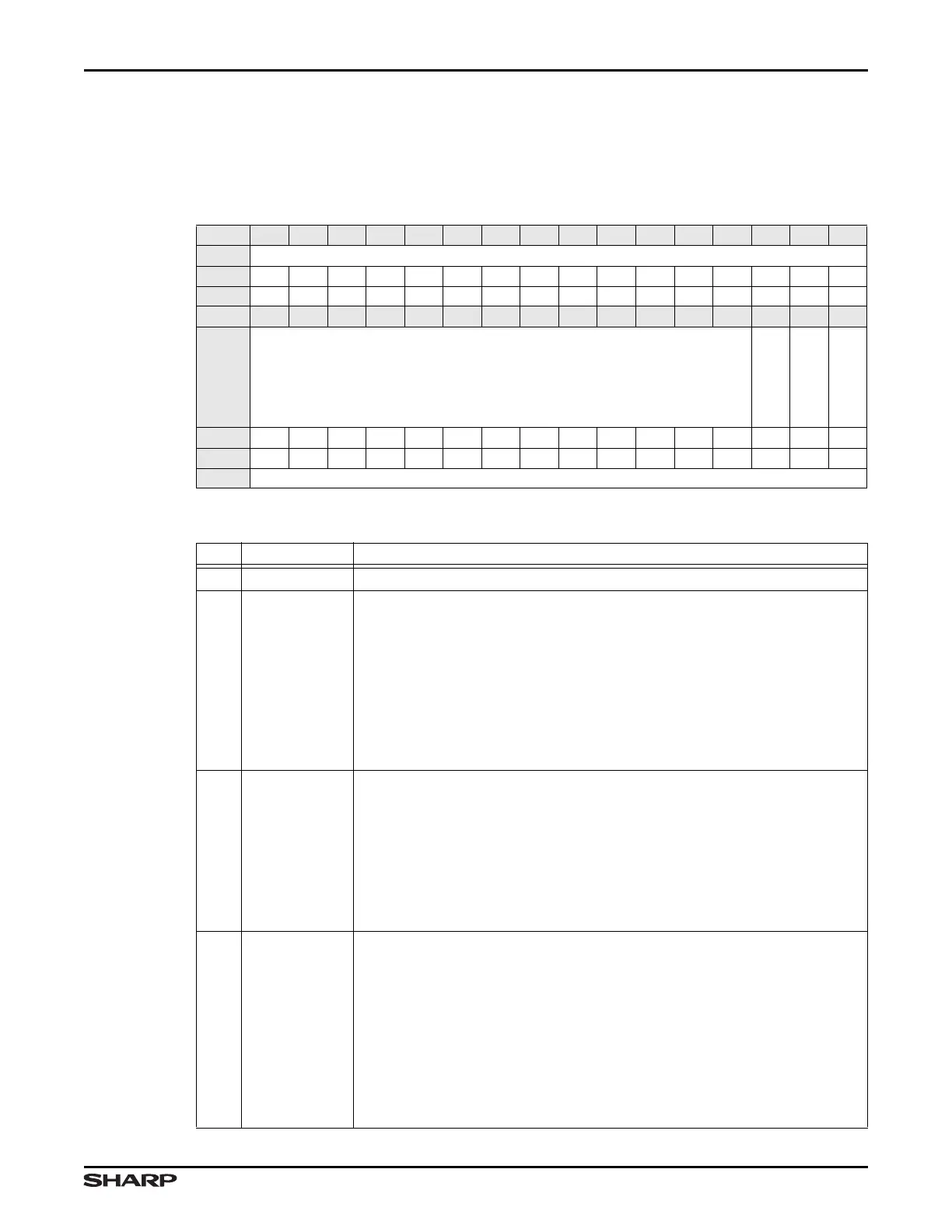

Table 6-18. RXSTATUS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

RXCOVERRUN

FRMREC

BUFNOTAVAIL

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW

ADDR 0xFFFC7000 + 0x20

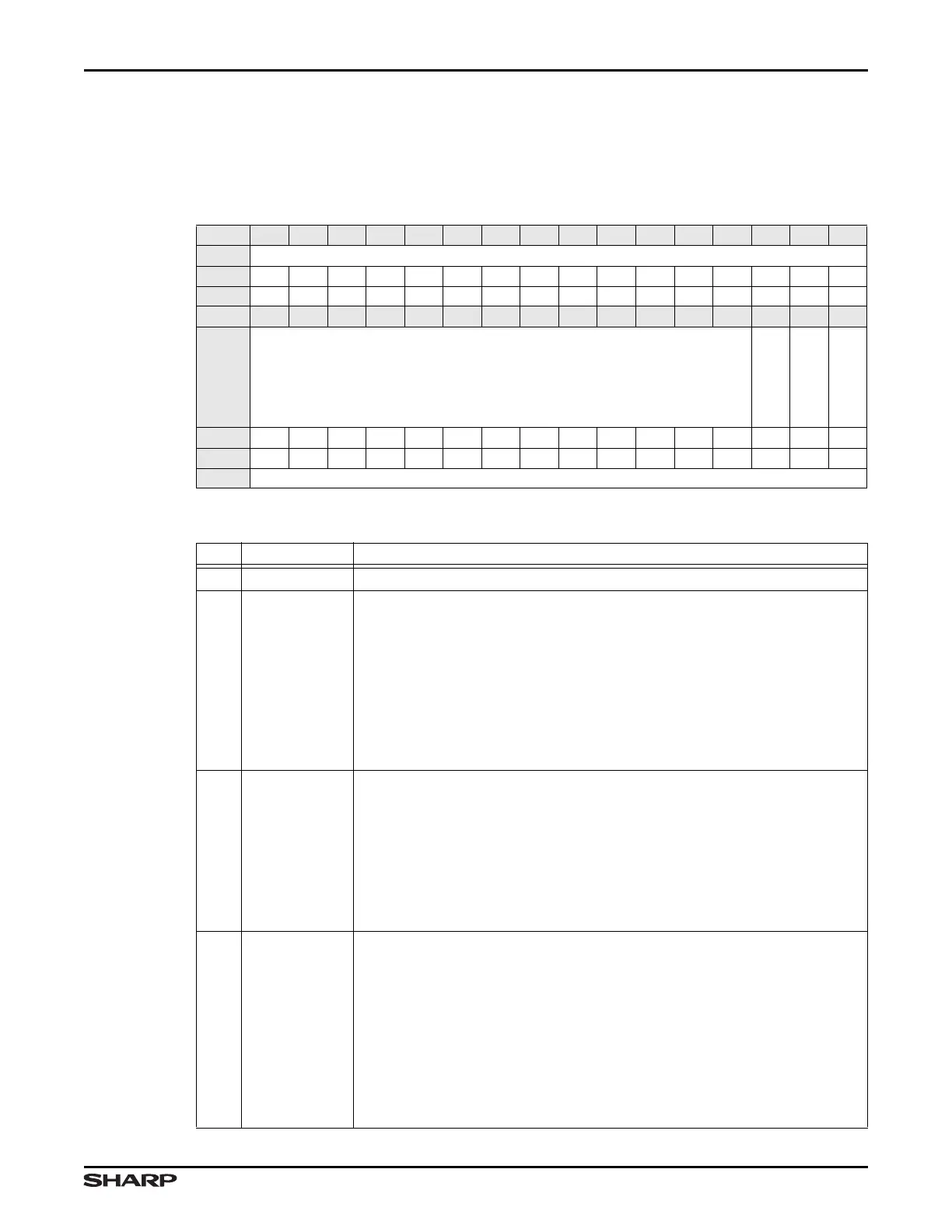

Table 6-19. RXSTATUS Fields

BITS NAME FUNCTION

31:3 /// Reserved Reading returns 0. Write the reset value.

2 RXCOVERRUN

Receive Overrun The DMA Block was unable to store the receive frame to

memory. Either because the AHB bus was not granted in time or because a ‘Not

OK’ response was returned. The buffer will be recovered if this happens.

Read:

1 = DMA unable to store receive frame

0 = Normal operation

Write:

1 = Reset bit to 0

0 = No effect

1 FRMREC

Frame Received Indicates that one or more frames have been received and

placed in memory.

Read:

1 = One or more frames have been received and placed in memory

0 = No received frames

Write:

1 = Reset bit to 0

0 = No effect

0 BUFNOTAVAIL

Buffer Not Available An attempt was made to get a new buffer and the pointer

indicated that it was owned by the processor. The DMA will reread the pointer each

time a new frame starts until a valid pointer is found. This bit will be 1 at each attempt

that fails even if it has not had a successful pointer read since it has been cleared.

Read:

1 = Buffer not available

0 = Buffer available

Write:

1 = Reset bit to 0

0 = No effect

Loading...

Loading...