Ethernet MAC Controller LH79524/LH79525 User’s Guide

6-34 Version 1.0

6.3.2.11 Interrupt Mask Register (MASK)

The MASK register is a read-only register that shows the status of the interrupt based on

what has been written to the ENABLE and DISABLE registers. As all interrupts are dis-

abled following reset, the interrupt bits in this register are reset to 1.

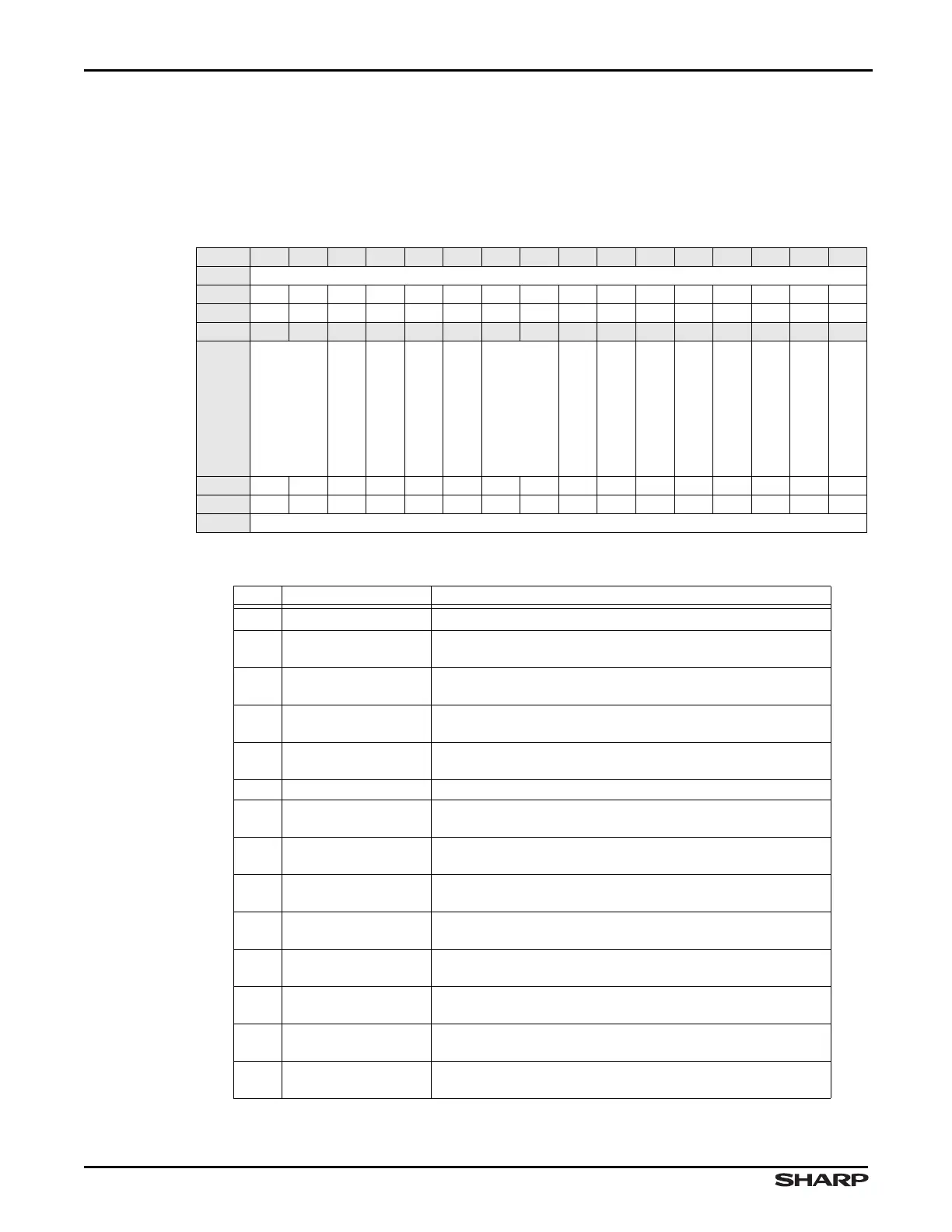

Table 6-26. MASK Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

PAUSETMZEROMSK

PAUSEFRRXMSK

NOTOKMSK

RECOVERRUNMSK

///

TXCOMPMSK

TXBUFEXHMSK

RETRYLMTEXMSK

TXBUFUNDERMSK

TXUSEDBITMSK

RXUSEDBITMSK

RXCOMPMSK

MNGDONEMSK

RESET 0011111111111111

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR 0xFFFC7000 + 0x30

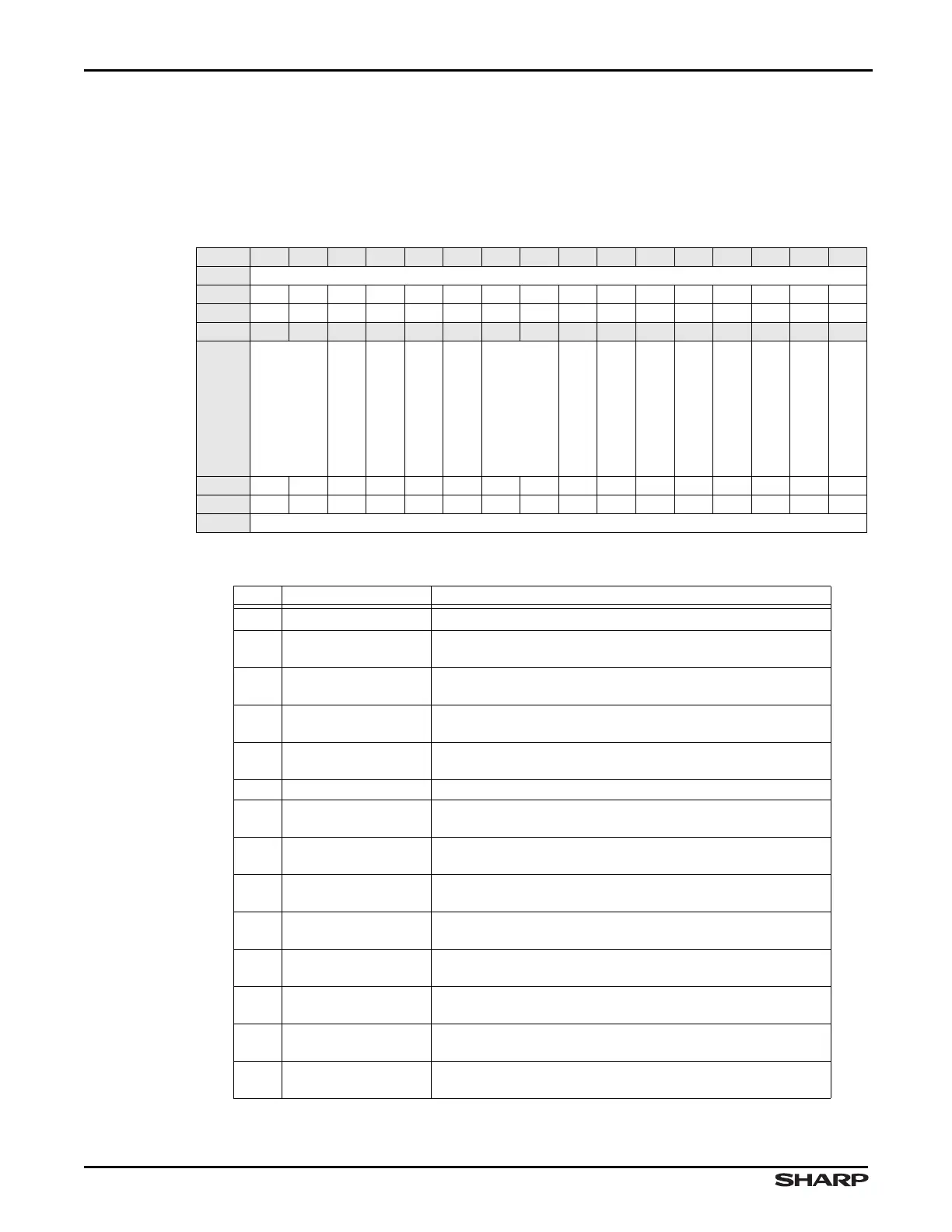

Table 6-27. MASK Fields

BITS NAME FUNCTION

31:14 /// Reserved Reading returns 0. Write the reset value.

13 PAUSETMZEROMSK

1 = Pause Time Zero Interrupt masked

0 = Unmasked

12 PAUSEFRRXMSK

1 = Pause Frame Received Interrupt masked

0 = Unmasked

11 NOTOKMSK

1 = Response ‘Not OK’ Interrupt masked

0 = Unmasked

10 RECOVERRUNMSK

1 = Receive Overrun Interrupt masked

0 = Unmasked

9:8 /// Reserved Reading returns 0. Write the reset value.

7 TXCOMPMSK

1 = Transmit Complete Interrupt masked

0 = Unmasked

6 TXBUFEXHMSK

1 = Transmit Buffers Exhausted In Mid-frame Interrupt masked

0 = Unmasked

5 RETRYLMTEXMSK

1 = Retry Limit Exceeded interrupt masked

0 = Unmasked

4 TXBUFUNDERMSK

1 = Transmit Buffer Underrun interrupt masked

0 = Unmasked

3TXUSEDBITMSK

1 = Transmit Used Bit Read interrupt masked

0 = Unmasked

2 RXUSEDBITMSK

1 = Receive Used Bit Read interrupt masked

0 = Unmasked

1 RXCOMPMSK

1 = Receive Complete interrupt masked

0 = Unmasked

0 MNGDONEMSK

1 = Management Done interrupt masked

0 = Unmasked

Loading...

Loading...