LH79524/LH79525 User’s Guide External Memory Controller

Version 1.0 7-33

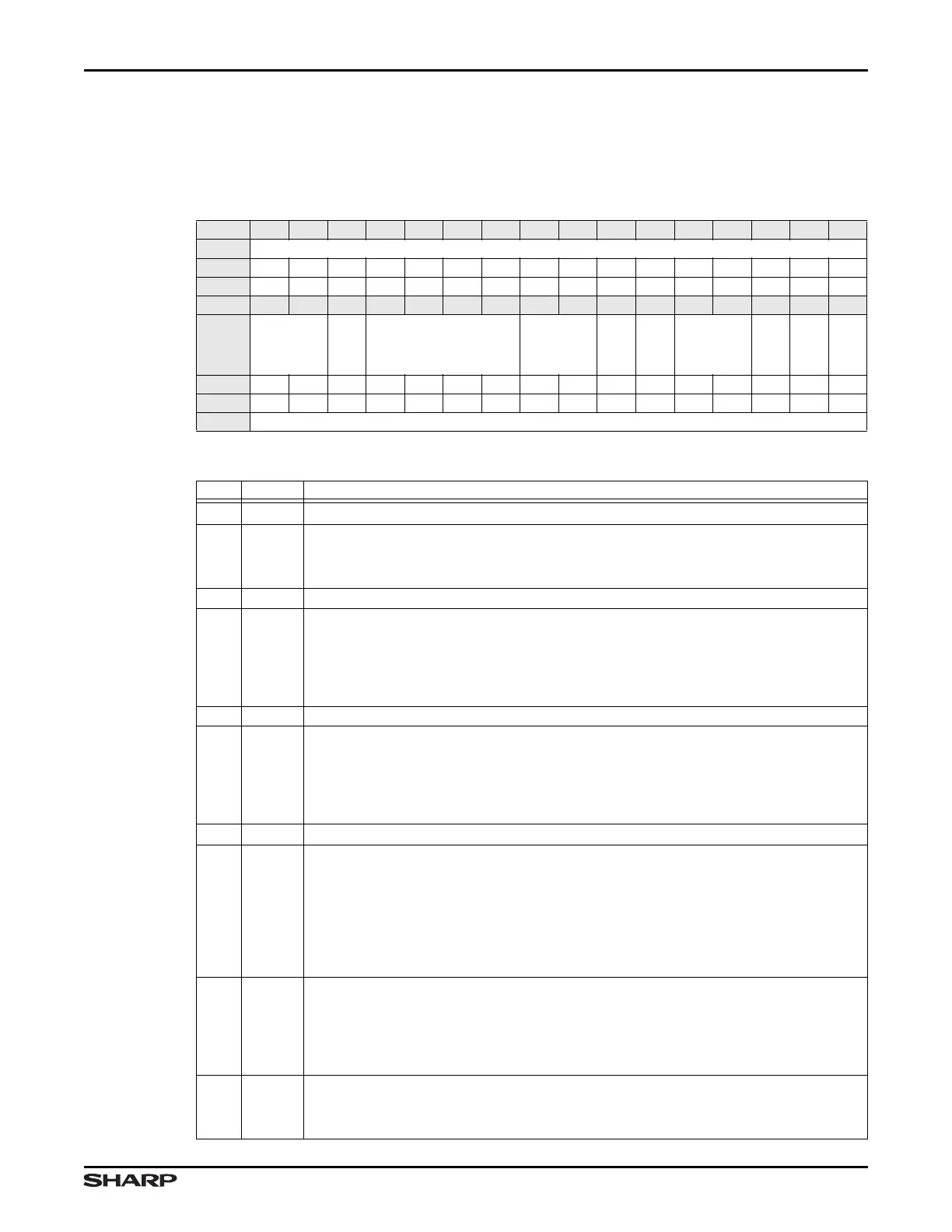

7.5.2.4 Dynamic Memory Control Register (DYNMCTRL)

The Dynamic Memory Control Register is used to control dynamic memory operation. The

control bits can be altered during normal operation.

Table 7-17. DYNMCTRL Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// DP /// INIT ///

MEMCC

/// SR CS CE

RESET 0000000000000110

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFF1000 + 0x020

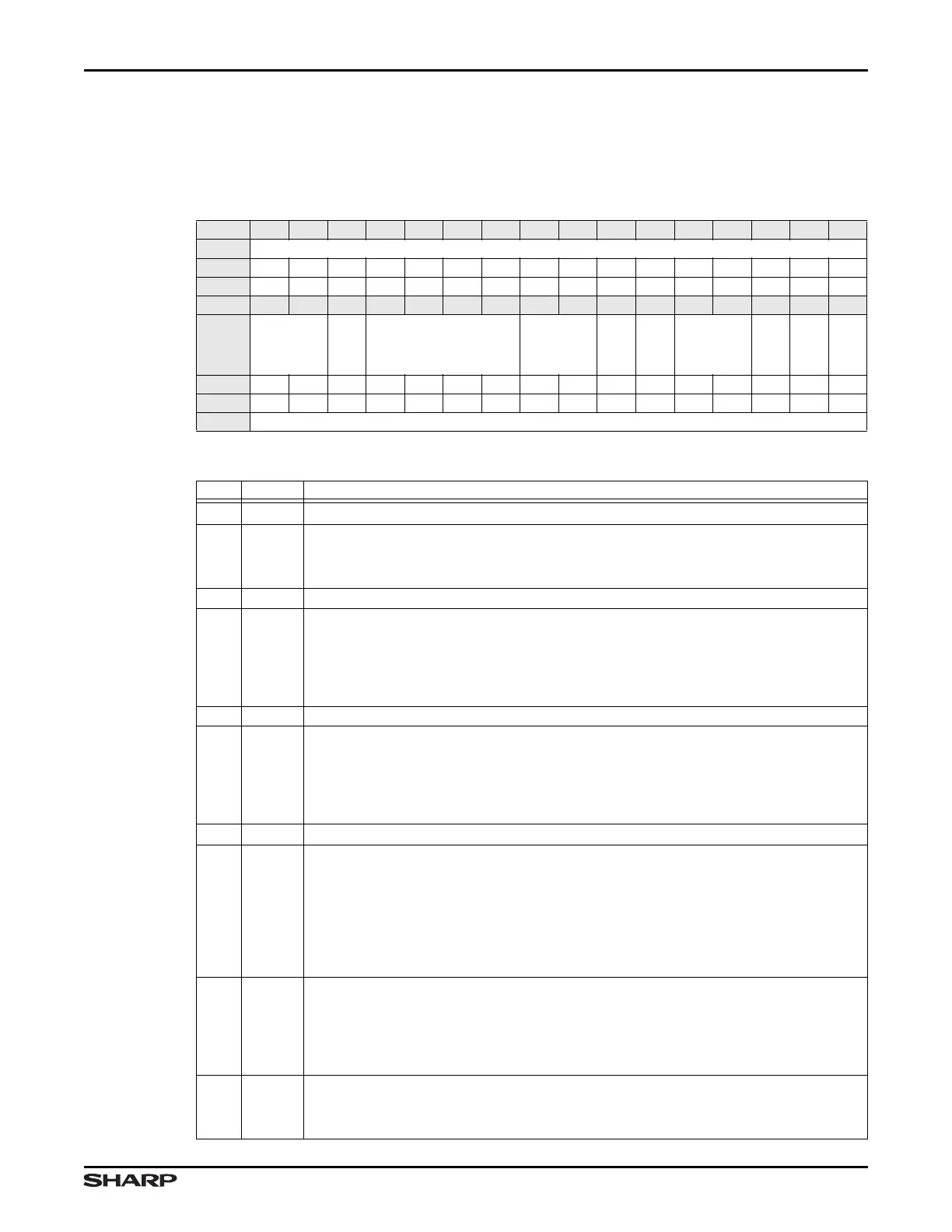

Table 7-18. DYNMCTRL Fields

BITS NAME FUNCTION

31:14 /// Reserved Reading returns 0. Write the reset value.

13 DP

Low-Power SDRAM Deep-Sleep Mode

1 = Enter deep power down mode

0 = Normal operation

12:9 /// Reserved Reading returns 0. Write the reset value.

8:7 INIT

SDRAM Initialization

00 = issue SDRAM NORMAL operation command

01 = issue SDRAM MODE command

10 = issue SDRAM PALL (precharge all) command

11 = issue SDRAM NOP (no operation) command

6///Reserved Reading returns 0. Write the reset value.

5MEMCC

Memory Clock Control Disabling SDCLK can be performed if there are no SDRAM

memory transactions. When enabled, this field can be used in conjunction with the dynamic

memory clock control (CS) field.

1 = SDCLK disabled

0 = SDCLK enabled

4:3 /// Reserved Reading returns 0. Write the reset value.

2SR

Self-Refresh Request Software can command the EMC into self-refresh by writing

a 1 to this bit. Writing 0 to this bit returns the memory controller to normal mode. The Self-

refresh Acknowledge bit (SA) in the Status register must be polled to determine the current

operating mode of the memory controller. Note that static memory may be accessed nor-

mally while dynamic memory is in self-refresh mode.

1 = Enter Self-Refresh Mode

0 = Normal Mode

1CS

Dynamic Memory Clock Select When clock control is 0 the output clock SDCLK is

stopped when there are no SDRAM transactions. The clock is also stopped during self-

refresh mode.

1 = SDCLK runs continuously

0 = SDCLK stops when all SDRAMs are idle and during self-refresh mode.

0CE

Dynamic Memory Clock Enable Clock enable must be HIGH during SDRAM initialization

1 = All clock enables are driven HIGH continuously

0 = Clock enable signal of idle devices are deasserted to save power

Loading...

Loading...