Reset, Clock, and Power Controller LH79524/LH79525 User’s Guide

13-34 Version 1.0

13.2.2.23 USB PLL Control Register (USBPLLCTL)

This register controls the USB PLL frequency and power down. The USB PLL frequency

is calculated by:

The maximum USB PLL frequency is 304.819 MHz.

Since the jitter is better with the PLL running above 100 MHz, it is best to program the PLL

to a frequency greater than 100 MHz and divide it by four using the USBPRE:USBDIV bit.

Here is a programming example using the typical crystal frequency of 11.2896 MHz:

Target frequency (48 MHz) × 4 = 192 MHz

Program USBLOOPDIV = 17 and USBPREDIV = 1

47.9808 ÷ 48.000 MHz = 0.04% Well within USB 2.0 Specification of ±0.25%

192 MHz = (11.2896 MHz × USLOOPDIV) ÷ USBPREDIV

192 MHz ÷ 11.2896 MHz = USBLOOPDIV ÷ USBPREDIV = 17.0068

(11.2896 MHz ÷ 17)/1 = 191.9232 MHz

191.9232 MHz/(USBDIV = 4) = 47.9808 MHz

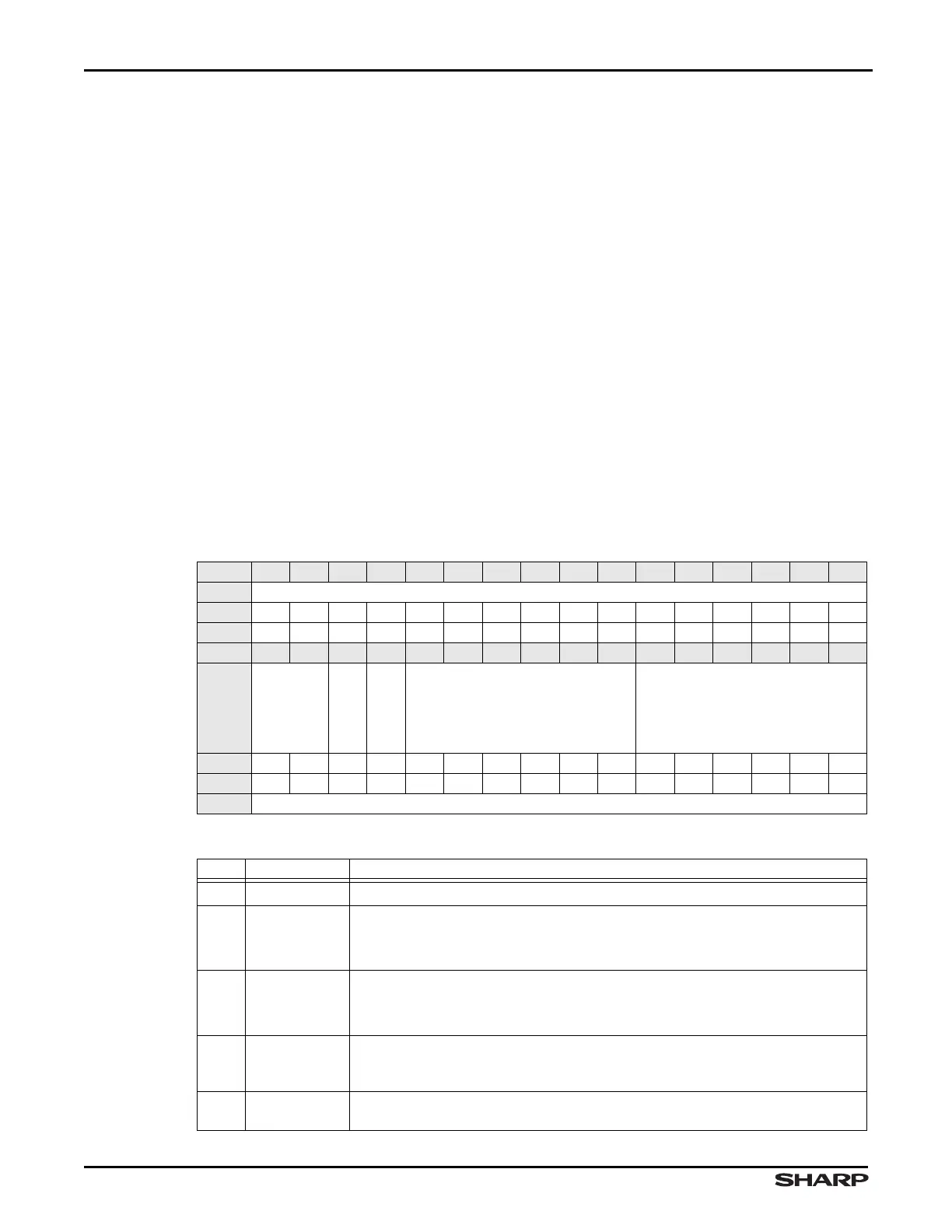

Table 13-54. USBPLLCTL Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

USBPDN

USBFRANGE

USBPREDIV USBLOOPDIV

RESET 0010000001000101

RW RO RO RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFE2000 + 0xC4

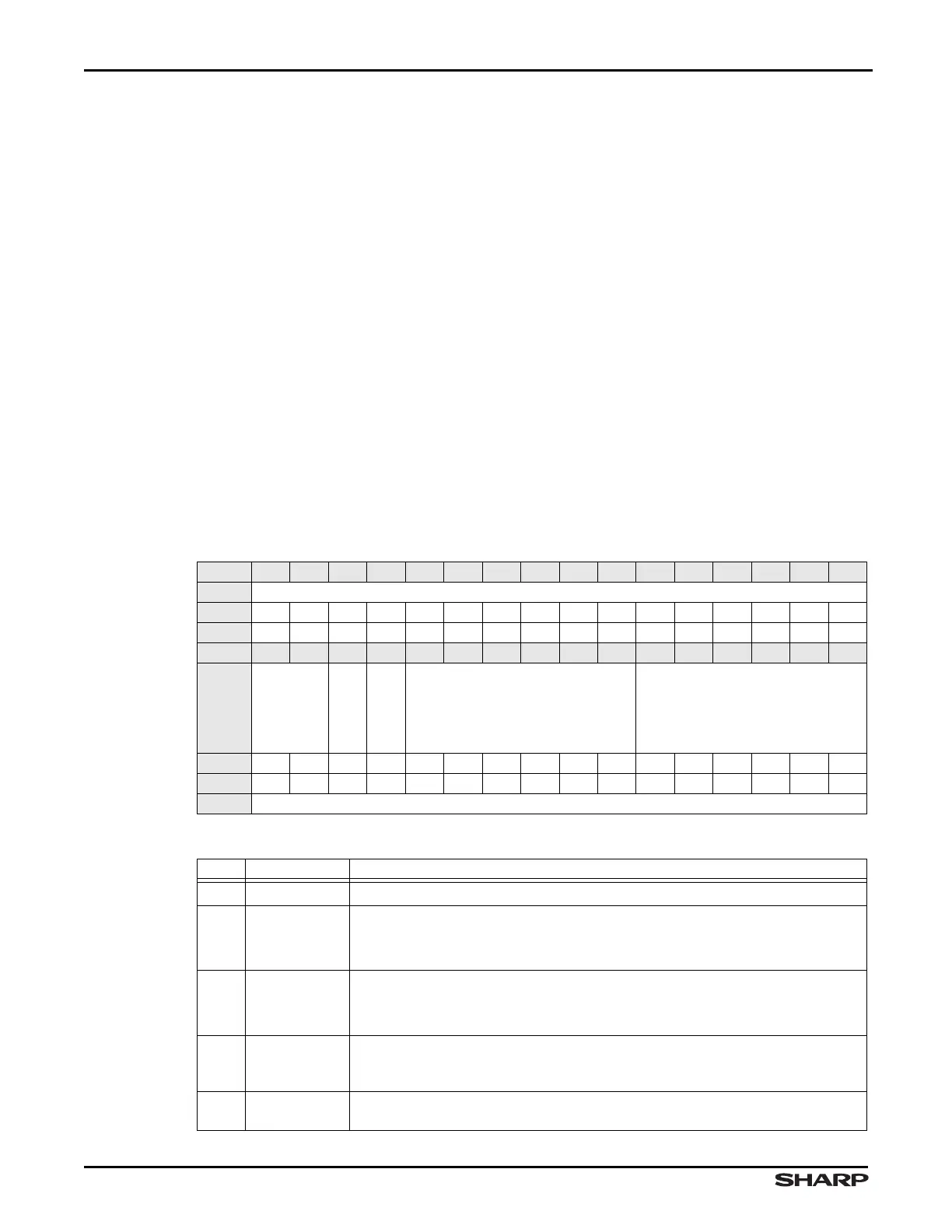

Table 13-55. USBPLLCTL Fields

BITS NAME DESCRIPTION

31:14 /// Reserved Writing to these bits has no effect. Reading returns 0.

13 USBPDN

USB PLL Power Down

1 = USB PLL Active

0 = USB PLL Powered Down

12 USBFRANGE

USB PLL Output Frequency Range Select

1 = 100 MHz - 304.819 MHz (best jitter performance achieved)

0 = 20 MHz - 100 MHz

11:6 USBPREDIV

USB PLL Pre-Divider Prescales the USB PLL Reference clock. The divisor

chosen must satisfy the equation:

(System Clock Oscillator frequency)

÷ (USBPREDIV) ≥ 5 MHz

5:0 USBLOOPDIV

USB PLL Loop-Divider Prescales the USB PLL Feedback clock. The divisor can

be programmed from 1 to 63.

USBPLLFrequency

SystemClockOscillatorFrequency()USBLOOPDIV×

USBPREDIV

---------------------------------------------------------------------------------------------------------------------------------------------------------

⎝⎠

⎛⎞

=

Loading...

Loading...