LH79524/LH79525 User’s Guide I

2

C Module

Version 1.0 9-7

9.2.2 Register Definitions

9.2.2.1 I

2

C Configuration Register (ICCON)

The ICCON register allows controlling the operating mode of the I

2

C Module, operating

parameters, and contains the flags used to start a transfer and to set the data direction.

Not all bits are active in every operating mode. Check the individual bit description to

determine if the bit is active during a particular operating mode.

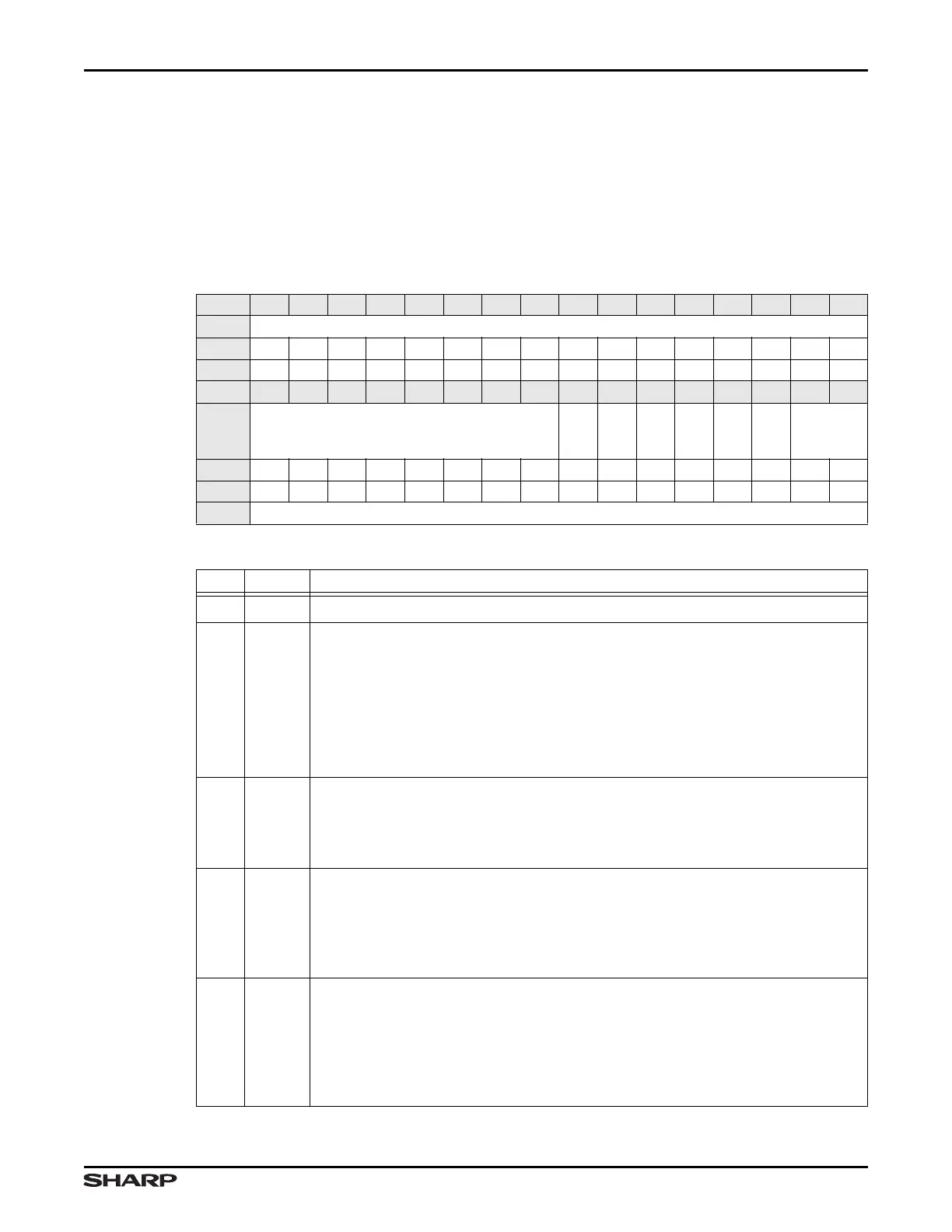

Table 9-4. ICCON Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

SABT

RWC

STOP

START

SPEED

I2CEN

MODE

RESET 0000000000001000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC5000 + 0x00

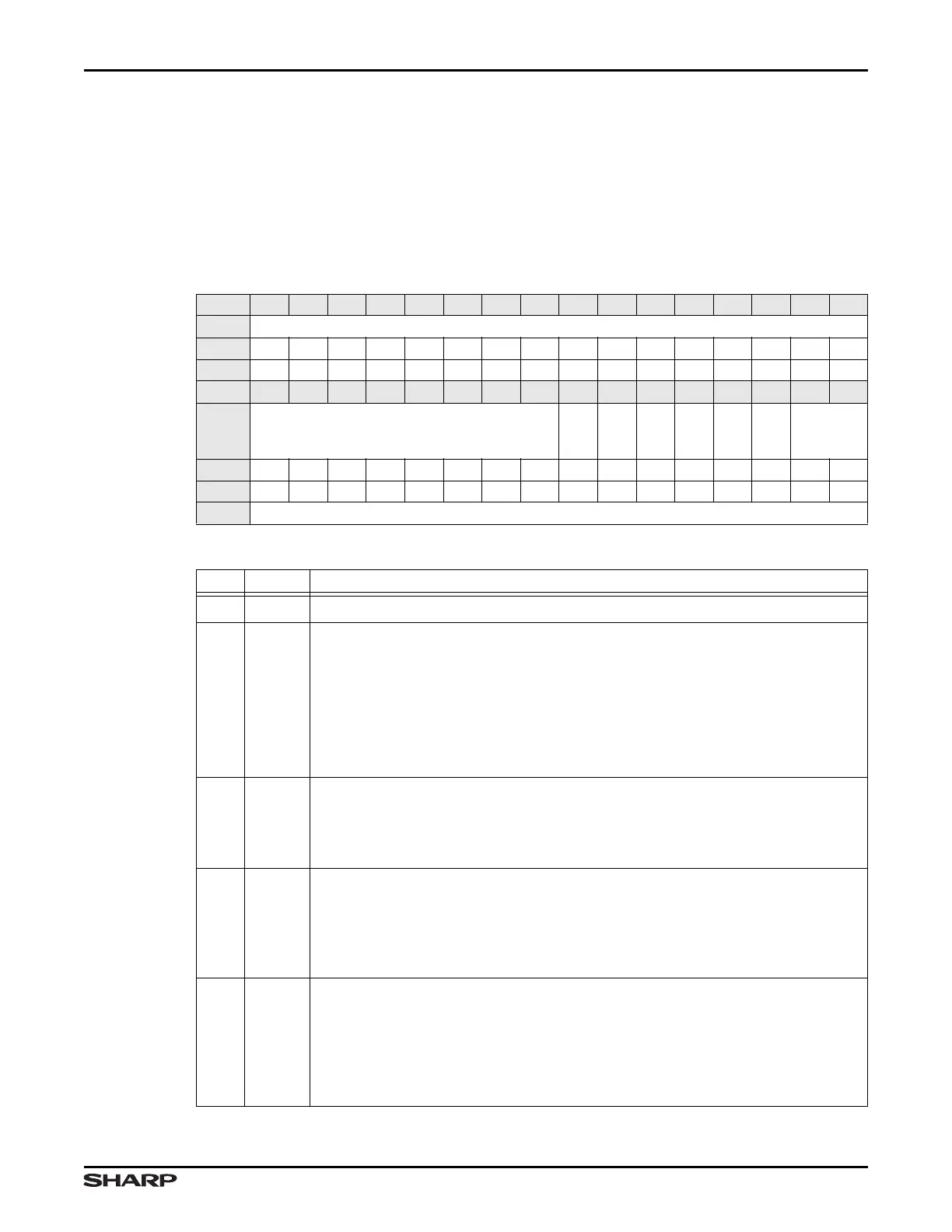

Table 9-5. ICCON Fields

BITS NAME DESCRIPTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7 SABT

Stop After Bus Transaction This bit is only active when in Master mode and

the ACK signal is not driven LOW by the Slave with which the I

2

C Module is

communicating.

Under those conditions, this bit is used to define whether or not a STOP Condi-

tion is generated after each bus transaction or not.

1 = No STOP Condition is generated

0 = An I

2

C STOP Condition is generated after each bus transaction

6RWC

Read/Write Control Only active in Master mode, it specifies direction for data

transfers.

1 = Read (Master receiver)

0 = Write (Master transmitter)

5STOP

Stop Transfer This bit is only active when in Master mode. It instructs the I

2

C

Module to terminate the data transfer after the completion of the current transac-

tion. Once the transaction is terminated, this bit is automatically reset to 0.

1 = Terminate data transfer following current transaction completion

0 = Do not terminate data transfer if additional data is pending

4START

Start Transfer This bit is active in both Master and Slave modes. In Master

mode, this bit causes the I

2

C Module to commence a transaction on the I

2

C bus.

In Slave mode this bit causes the I

2

C Module to transmit a byte of data to the

Master. This bit is automatically reset to 0 at the completion of the transaction.

1 = (Master) Commence transaction; (Slave) transmit one data byte

0 = No action

Loading...

Loading...