Timers LH79524/LH79525 User’s Guide

15-18 Version 1.0

15.2.2.10 Timer 1 Status Register (STATUS1)

The Status Register bits contain the raw interrupt status of the various interrupt generators.

Raw interrupts reflect the state of the interrupt, whether or not it is enabled. To clear a

status bit, write a 1 to that bit. This action also clears the corresponding interrupt, with the

following exception: if the timer is stopped and the Timer 1 Compare Register (T1CMP0 or

T1CMP1) value matches the Timer 1 Counter Register (CNT1), the corresponding status

bit cannot be cleared until either the Timer 1 Compare Register or CNT1 value is changed.

Writing a 0 to any of the status bits has no effect. Similarly, writing a 1 to a bit that currently

reads as 0 (no interrupt assertion) does not affect the Status Register or interrupt.

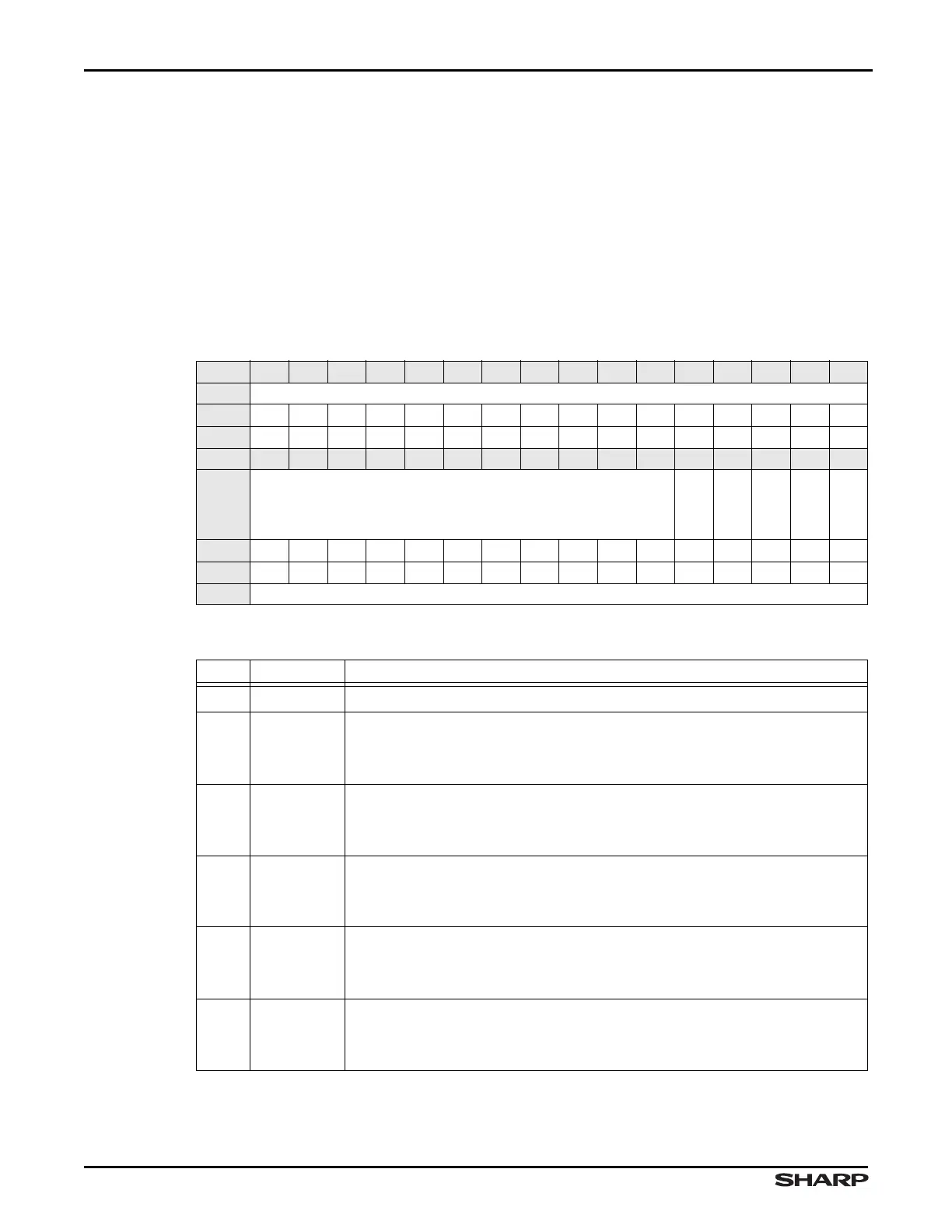

Table 15-22. STATUS1 Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

CAPB_ST

CAPA_ST

CMP1_ST

CMP0_ST

OVF_ST

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW RW

ADDR 0xFFFC4000 + 0x38

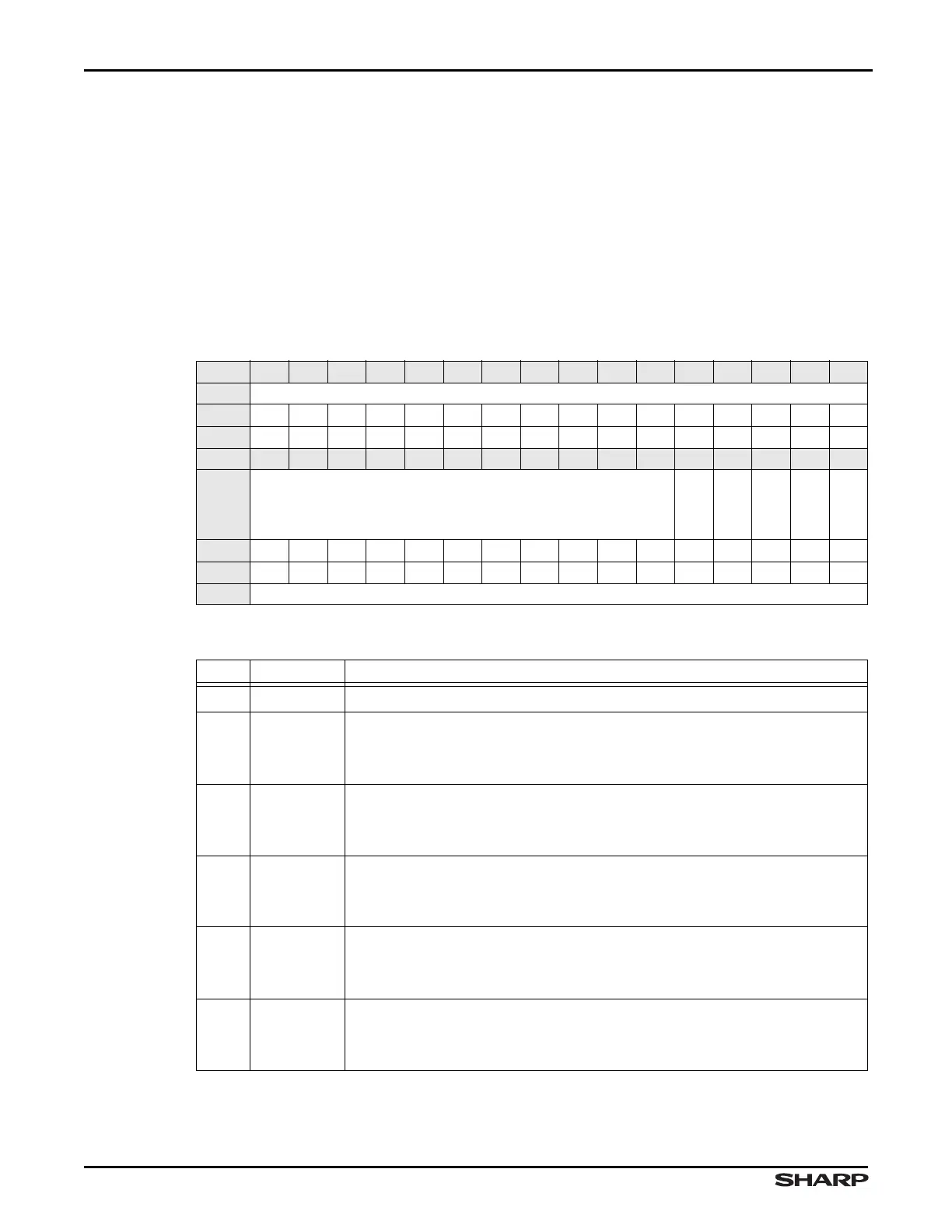

Table 15-23. STATUS1 Register Definitions

BITS NAME DESCRIPTION

31:5 ///

Reserved Reading this field returns 0. Write the reset value.

4 CAPB_ST

Timer 1 Capture B Status

1 = Read: Interrupt asserted; Write: Clear interrupt

0 = Read: No interrupt asserted; Write: No effect

3 CAPA_ST

Timer 1 Capture A Status

1 = Read: Interrupt asserted; Write: Clear interrupt

0 = Read: No interrupt asserted; Write: No effect

2 CMP1_ST

Timer 1 Compare 1 Status

1 = Read: Interrupt asserted; Write: Clear interrupt

0 = Read: No interrupt asserted; Write: No effect

1 CMP0_ST

Timer 1 Compare 0 Status

1 = Read: Interrupt asserted; Write: Clear interrupt

0 = Read: No interrupt asserted; Write: No effect

0OVF_ST

Timer 1 Overflow Status

1 = Read: Interrupt asserted; Write: Clear interrupt

0 = Read: No interrupt asserted; Write: No effect

Loading...

Loading...