LH79524/LH79525 User’s Guide Ethernet MAC Controller

Version 1.0 6-39

6.3.3.4 Multiple Collision Frames (MULTFRM)

This register counts the number of frames that experienced between two and 15 collisions

before successful transmission.

6.3.3.5 Frames Received OK (FRMRXOK)

This is a 24-bit register containing the number of good frames received. Good frames are

defined as having the address recognized and successfully copied to memory. A good

frame length is between 64 and 1,518 bytes (1,522 if NETCONFIG:RECBYTE is 1) and

has no FCS, alignment, or receive symbol errors.

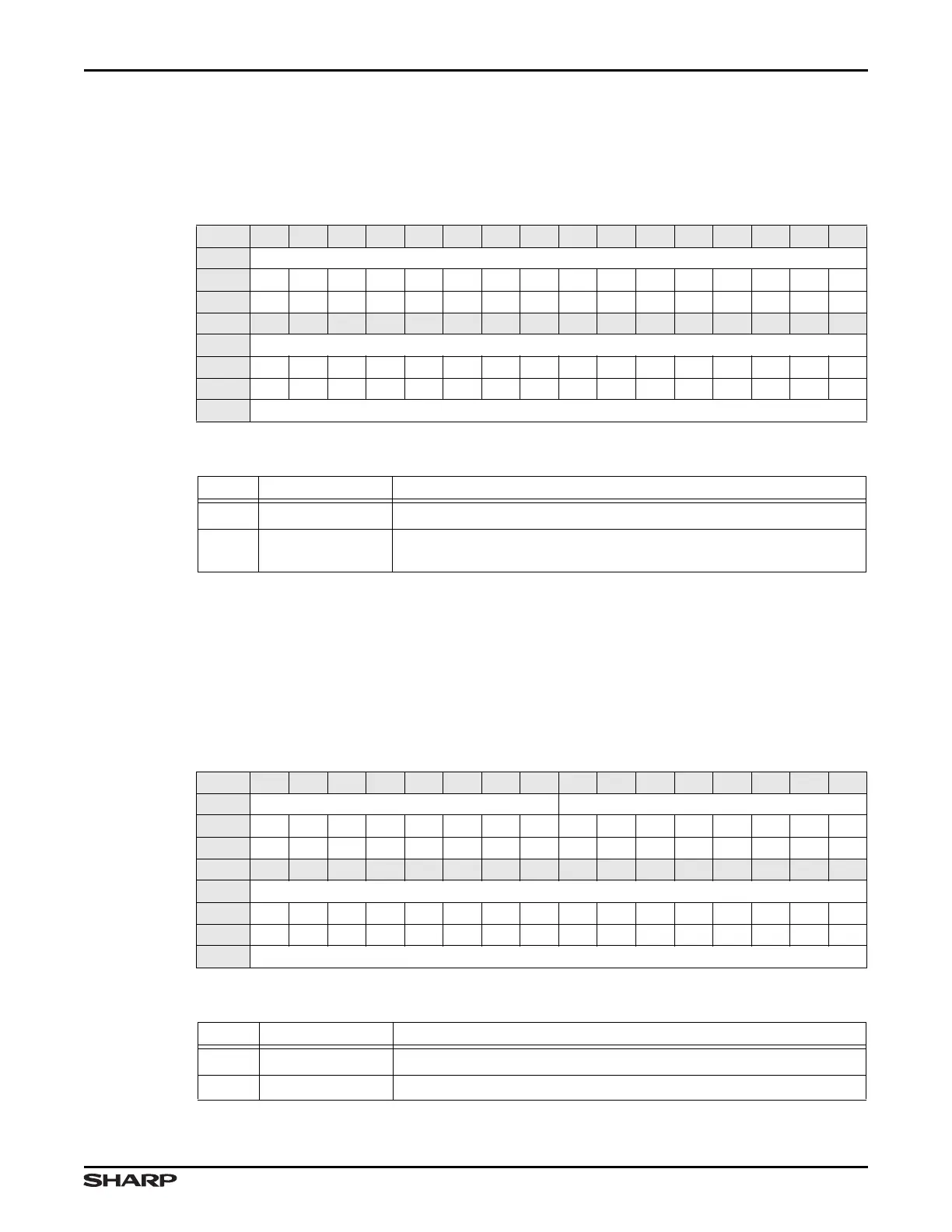

Table 6-40. MULTFRM Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD MULTFRM

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x48

Table 6-41. MULTFRM Fields

BITS NAME FUNCTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:0 MULTFRM

Multiple Collision Frames Contains the number of successfully-

transmitted frames that experienced between two and 15 collisions.

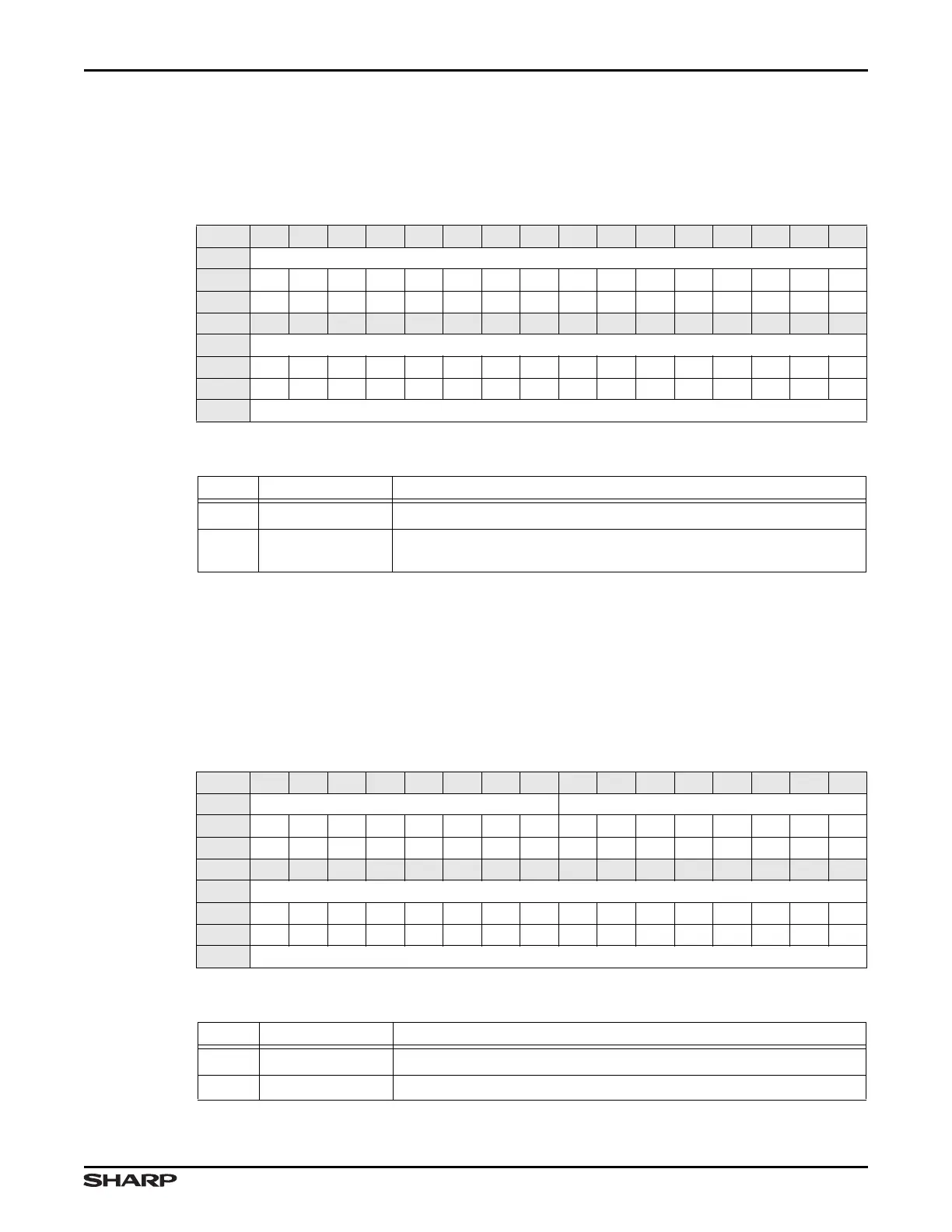

Table 6-42. FRMRXOK Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD /// FRMRXOK

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD FRMRXOK

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x4C

Table 6-43. FRMRXOK Fields

BITS NAME FUNCTION

31:24 /// Reserved Reading returns 0. Write the reset value.

23:0 FRMRXOK Frames Received OK Number of correctly received frames.

Loading...

Loading...