Direct Memory Access Controller LH79524/LH79525 User’s Guide

5-10 Version 1.0

6:5 SOBURST

Peripheral Burst Size Defines the number of peripheral data units in the

peripheral burst. Using the peripheral as the destination, the DMA interface

automatically reads the correct number of source words to compile a trans-

action. When stream 3 is configured as a memory-to-memory transfer,

SOBURST is the source-side burst length. Table 5-16 shows valid values.

4:3 SOSIZE

Source-to-DMA Data Width See Table 5-16. Note that Stream 0

(SSPRX) only supports half-word source data width.

2DEINC

Current Destination Register Increment Enables the Current

Destination Register increment after each DMA-to-destination data transfer.

1 = Current Destination Register is incremented

0 = Current Destination Register remains unchanged

1SOINC

Current Source Register Increment Enables a Current Source Register

increment after each source-to-DMA data transfer.

1 = Current Source Register increments as data transfers from a source to

the DMA. The value increments at the end of the address phase of the

AHB transfer

0 = Current Source Register remains unchanged, holding the same value

during the entire DMA transfer

0ENABLE

DMA Controller Enable/Disable Enables or disables the DMA Controller.

The Source Base, Destination Base, and Maximum Count Registers must be

set before the DMA is enabled. The state machine clears this bit when a data

transfer finishes. If the software resets this bit during a transfer, that stream

interface will be reset.

1 = DMA data transfer is enabled

0 = DMA data transfer is disabled

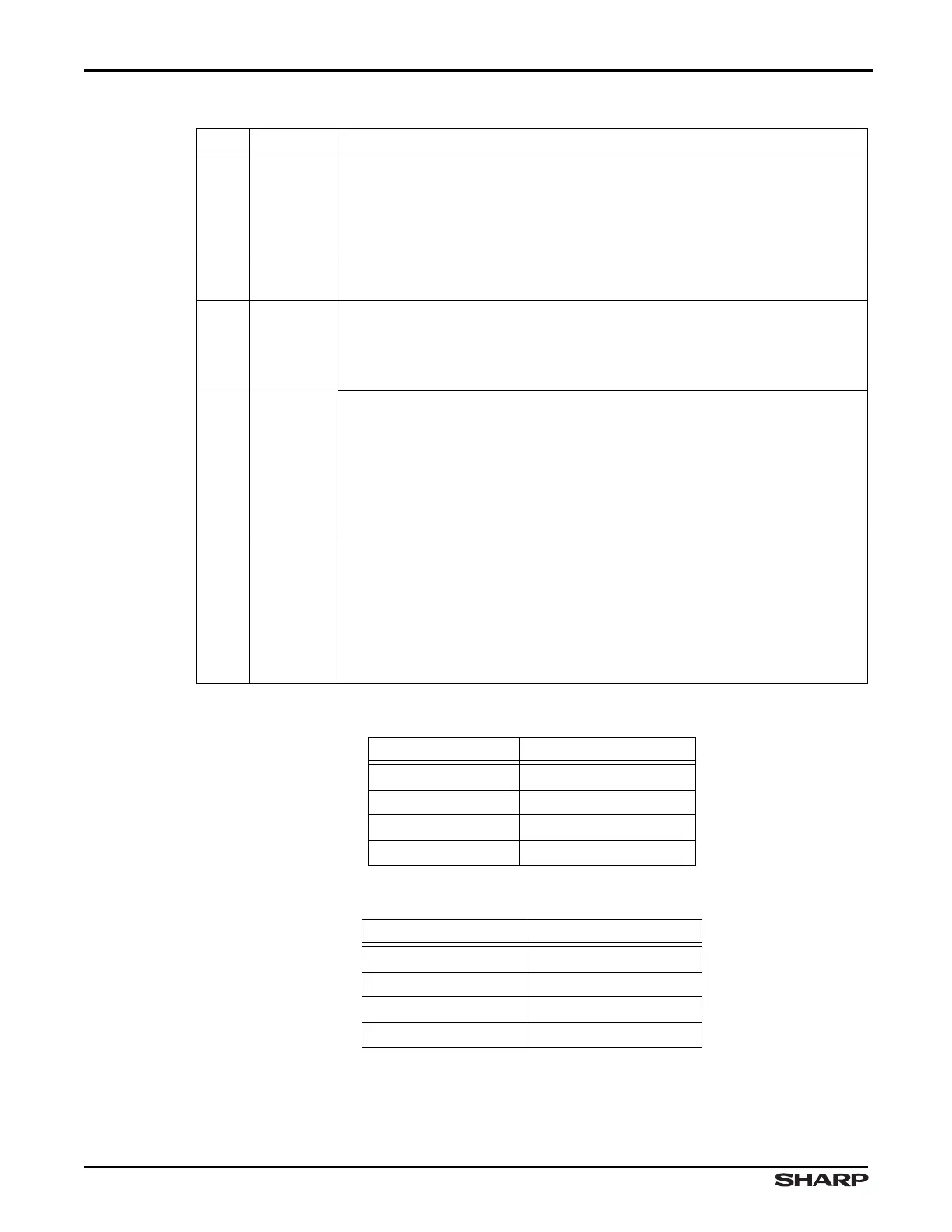

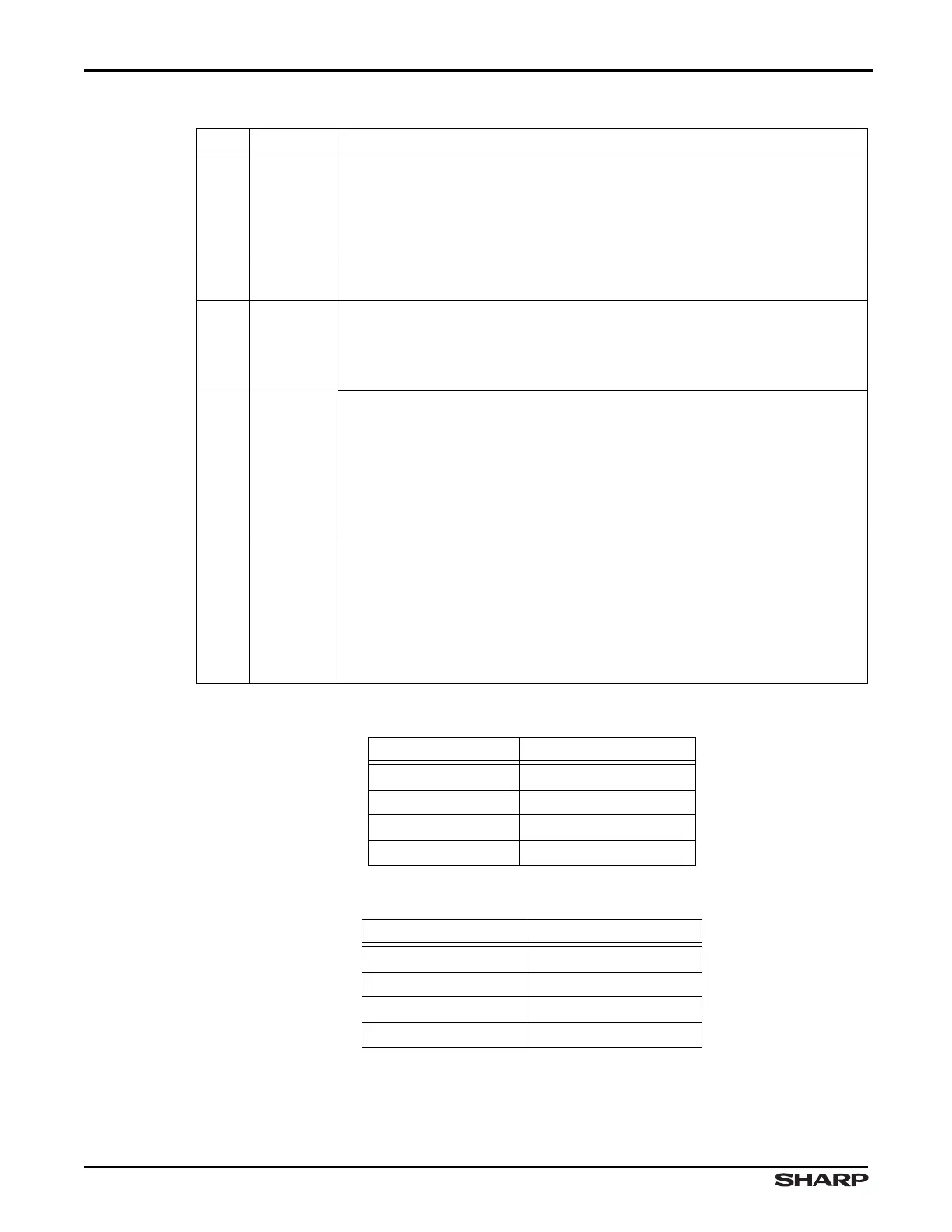

Table 5-16. DMA Data Width

SOSIZE/DESIZE AHB DATA WIDTH

00 1 byte

01 1 half-word (2 bytes)

10 1 word (4 bytes)

11 Reserved

Table 5-17. DMA Burst Size

SOBURST AHB BURST TYPE

00 Single

01 4

10 8

11 16

Table 5-15. CTRL Fields (Cont’d)

BIT NAME DESCRIPTION

Loading...

Loading...