External Memory Controller LH79524/LH79525 User’s Guide

7-28 Version 1.0

7.5 Register Reference

The base address for the EMC is 0xFFFF1000.

7.5.1 Memory Map

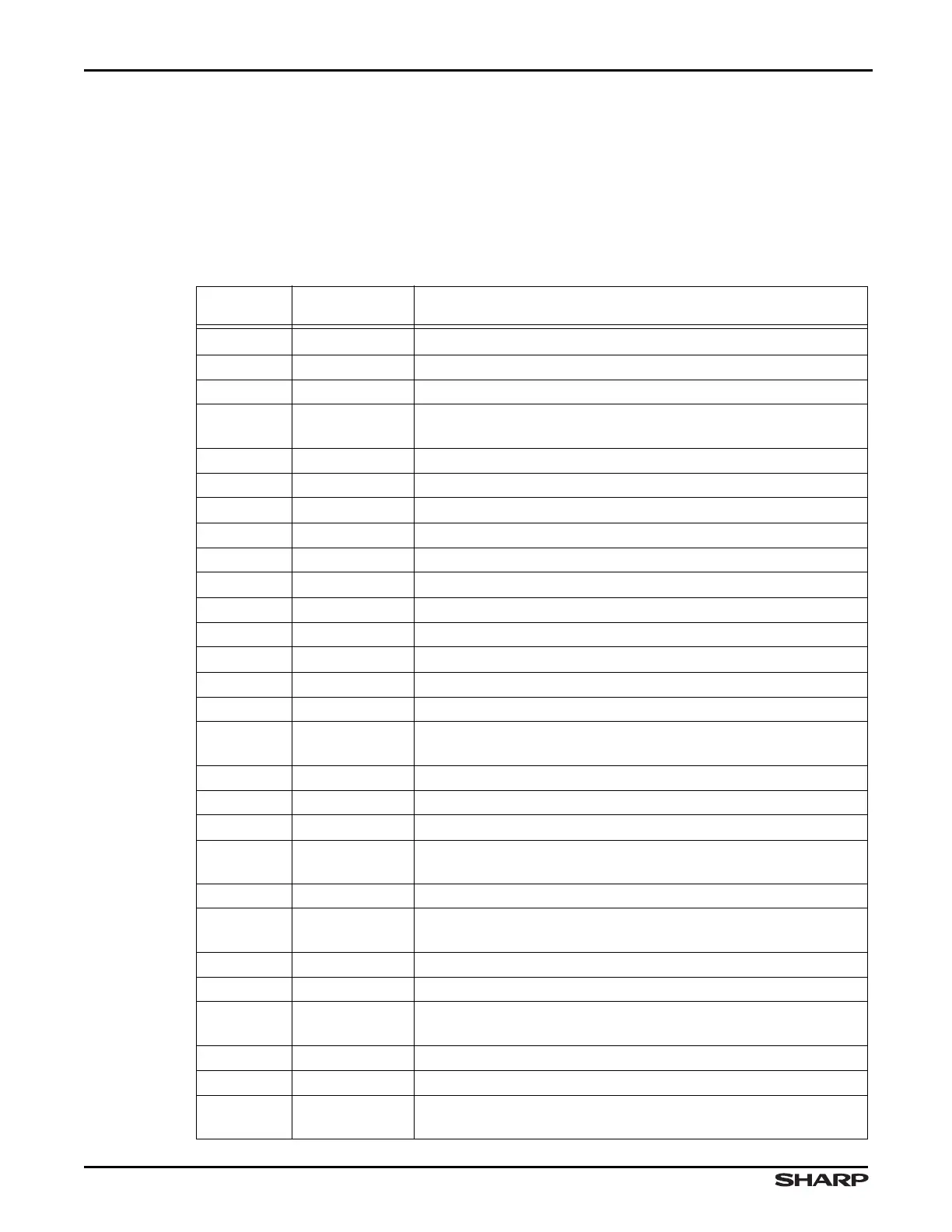

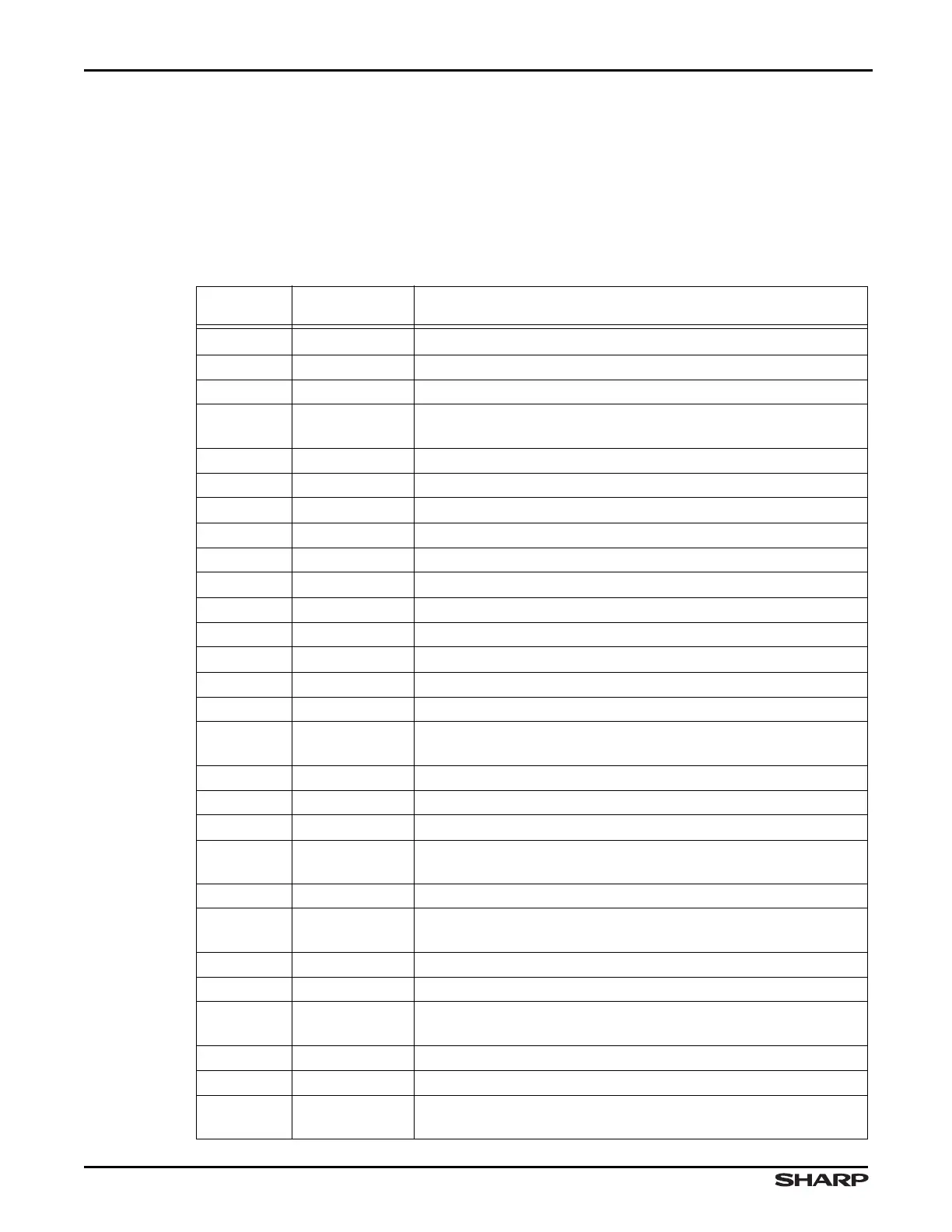

Table 7-10 Summarizes the EMC registers.

Table 7-10. External Memory Controller Register Summary

ADDRESS

OFFSET

REGISTER DESCRIPTION

0x000 CONTROL Control Register

0x004 STATUS Status Register

0x008 CONFIG Configuration Register

0x00C to

0x01C

/// Reserved

0x020 DYNMCTRL Dynamic Memory Control Register

0x024 DYNMREF Dynamic Memory Refresh Timer

0x028 DYNRCON Dynamic Memory Read Configuration Register

0x02C /// Reserved

0x030 PRECHARGE Dynamic Memory Precharge Command Period

0x034 DYNM2PRE Dynamic Memory Active to Precharge Command Period

0x038 REFEXIT Dynamic Memory Self-Refresh Exit Time

0x03C DOACTIVE Dynamic Memory Last Data Out to Active Time

0x040 DIACTIVE Dynamic Memory Data-In to Active Command Time

0x044 DWRT Dynamic Memory Write Recovery Time

0x048 DYNACTCMD Dynamic Memory Active to Active Command Period

0x04C DYNAUTO

Dynamic Memory Auto-Refresh Period, and Auto-Refresh to

Active Command Period

0x050 DYNREFEXIT Dynamic Memory Exit Self-Refresh to Active Command Time

0x054 DYNACTIVEAB Dynamic Memory Active Bank A to Active Bank B Time

0x058 DYNAMICMRD Dynamic Memory Load Mode Register to Active Command Time

0x05C to

0x07C

/// Reserved

0x080 WAIT Static Memory Extended Wait

0x084 to

0x0FC

/// Reserved

0x100 DYNCFG0 Dynamic Configuration Register for nDCS0

0x104 DYNRASCAS0 Dynamic Memory RAS and CAS Delay for nDCS0

0x108 to

0x11C

/// Reserved

0x120 DYNCFG1 Dynamic Configuration Register for nDCS1

0x124 DYNRASCAS1 Dynamic Memory RAS and CAS Delay for nDCS1

0x128 to

0x1FC

/// Reserved

Loading...

Loading...