LH79524/LH79525 User’s Guide Analog-to-Digital Converter/Brownout Detector

Version 1.0 2-21

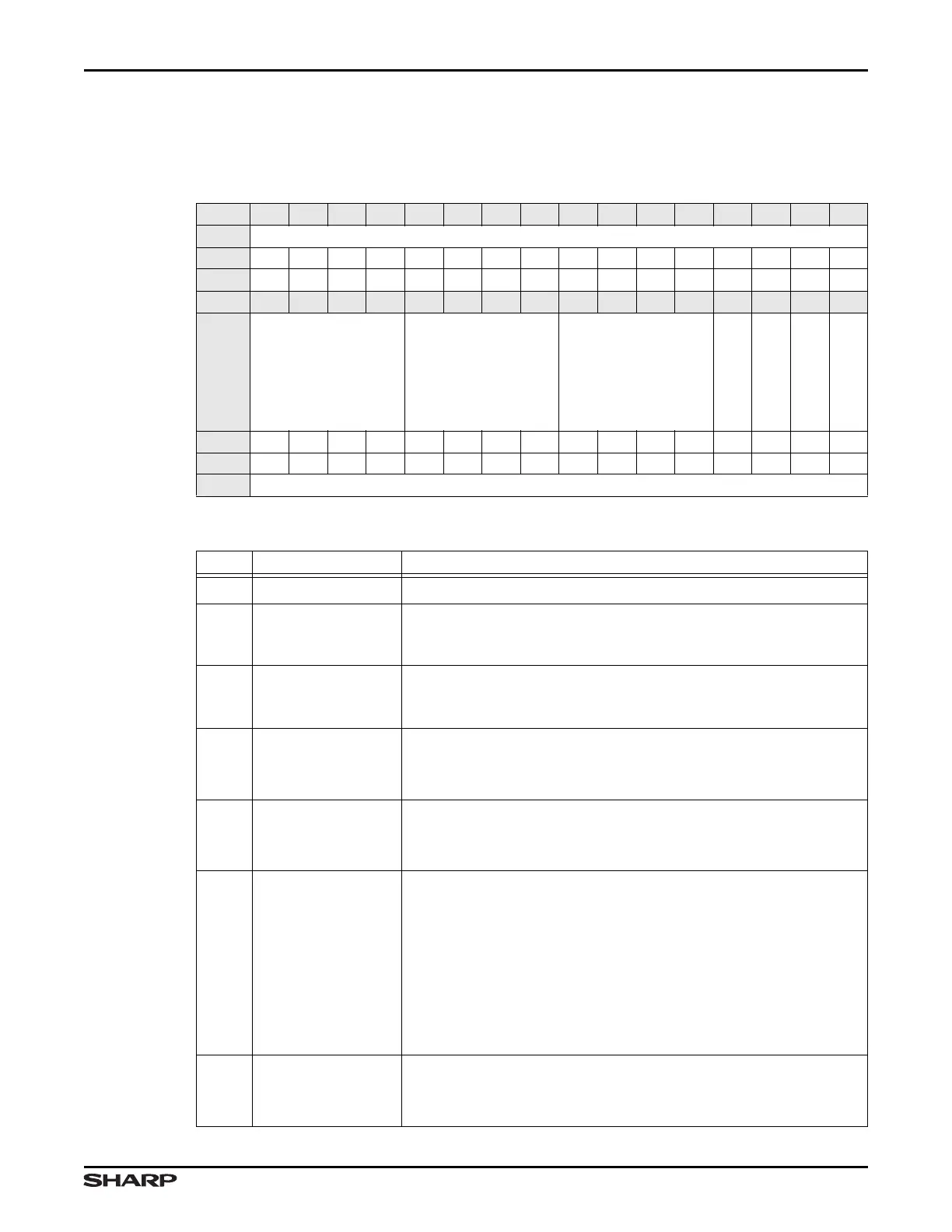

2.2.2.9 FIFO Status Register (FS)

FS is the FIFO Status Register. This Read Only register indicates the FIFO fill status.

Table 2-20. FS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// WRPTR RDPTR FFF

FEMPTY

FOVRNDET

FGTEWATERMRK

RESET 0000000000000100

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR 0xFFFC3000 + 0x20

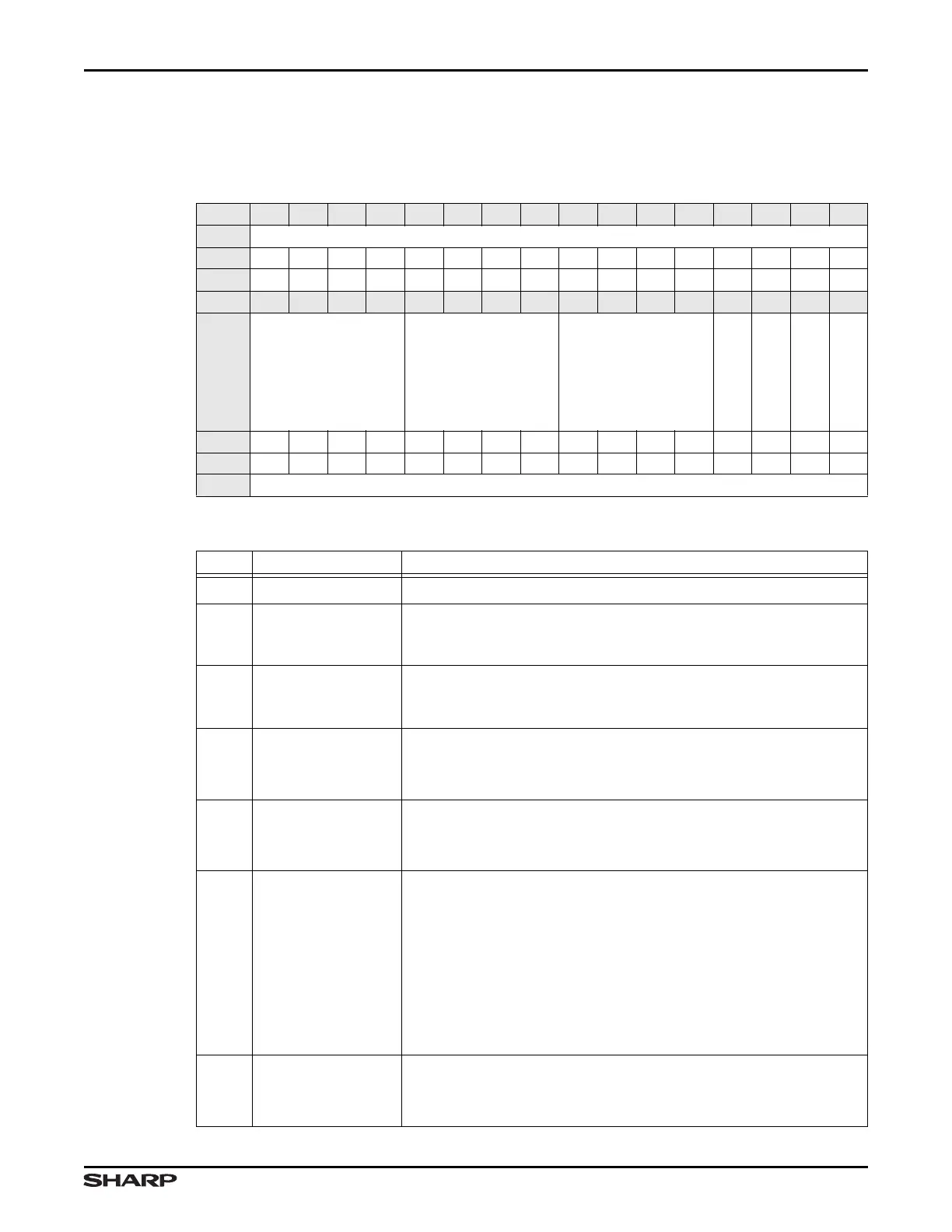

Table 2-21. FS Fields

BIT NAME DESCRIPTION

31:12 /// Reserved Reading returns 0. Write the reset value.

11:8 WRPTR

Write Pointer FIFO Location Contains the index of the memory

location in the result FIFO array where the next measurement

result will be stored.

7:4 RDPTR

Read Pointer FIFO Location Contains the index to the location

in the result FIFO array where the next measurement result will be

read. Reads from the RR register increment this value.

3 FFF

FIFO Full

1 = FIFO is full

0 = FIFO is not full

2 FEMPTY

FIFO Empty

1 = FIFO is empty

0 = FIFO is not empty

1 FOVRNDET

FIFO Overrun Status Bit This bit is 1 when the receive logic tries

to place data into the FIFO after it has been completely filled. When

new data is received, the FOVRNDET bit is asserted and the newly

received data is discarded. This process repeats for each time new

data is received, until at least one empty FIFO entry exists. When

FOVRNDET is set to 1, an interrupt request is generated.

1 = Logic tried to place data into a full receive FIFO and is

requesting an interrupt

0 = FIFO has not experienced an overrun

0 FGTEWATERMRK

FIFO at Watermark

1 = FIFO is at or above watermark level

0 = FIFO has fewer entries than the watermark level

Loading...

Loading...