LH79524/LH79525 User’s Guide UARTs

Version 1.0 16-11

16.3.2.3 Flag Register (UARTFR)

UARTFR is the Flag Register. After System Reset, TXFF, RXFF, and BUSY are 0, and

TXFE and RXFE are 1.

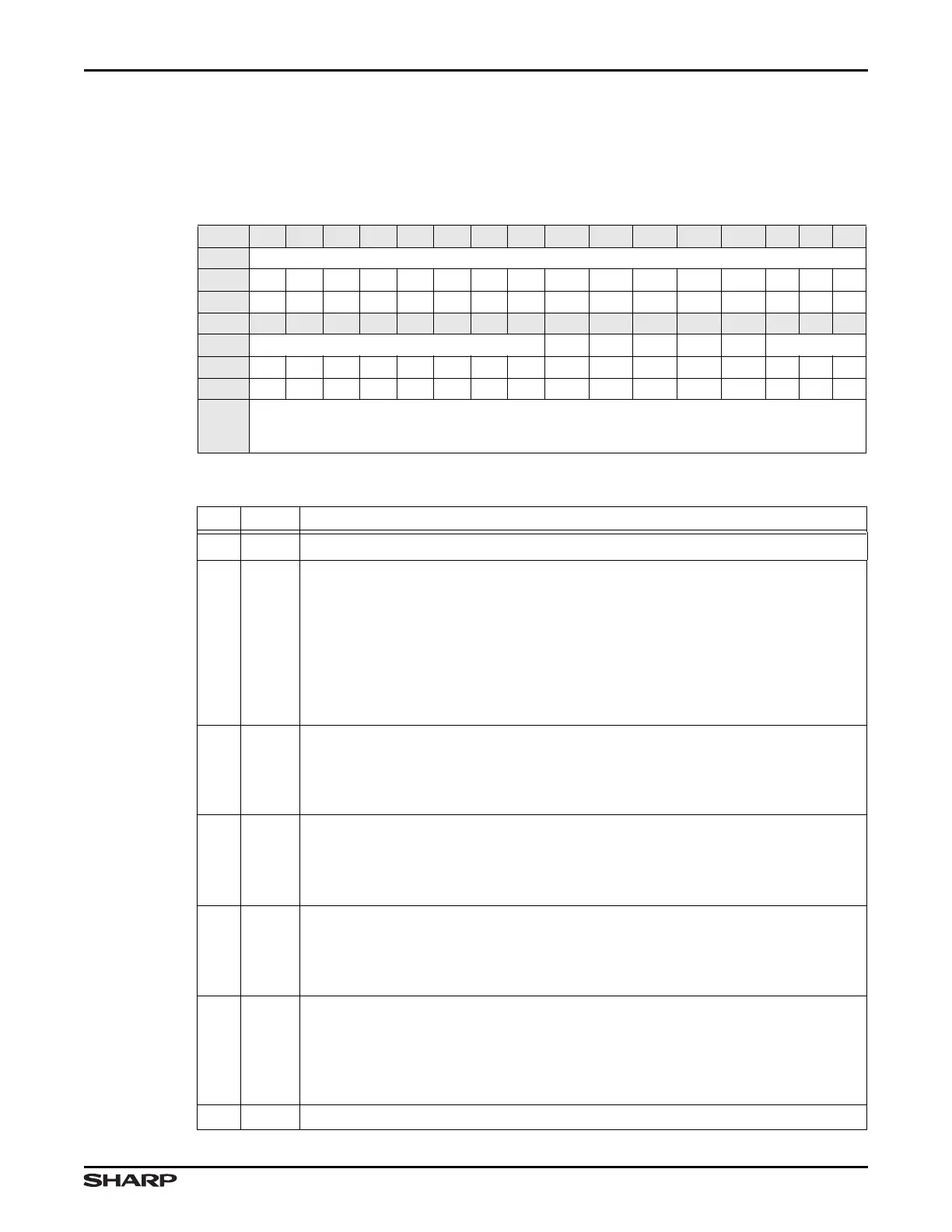

Table 16-10. UARTFR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 00001011 0 0 0 0 0000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// TXFE RXFF TXFF RXFE BUSY ///

RESET 00000000 1 0 0 1 0000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR

UART 0: 0xFFFC0000 + 0x018

UART 1: 0xFFFC1000 + 0x018

UART 2: 0xFFFC2000 + 0x018

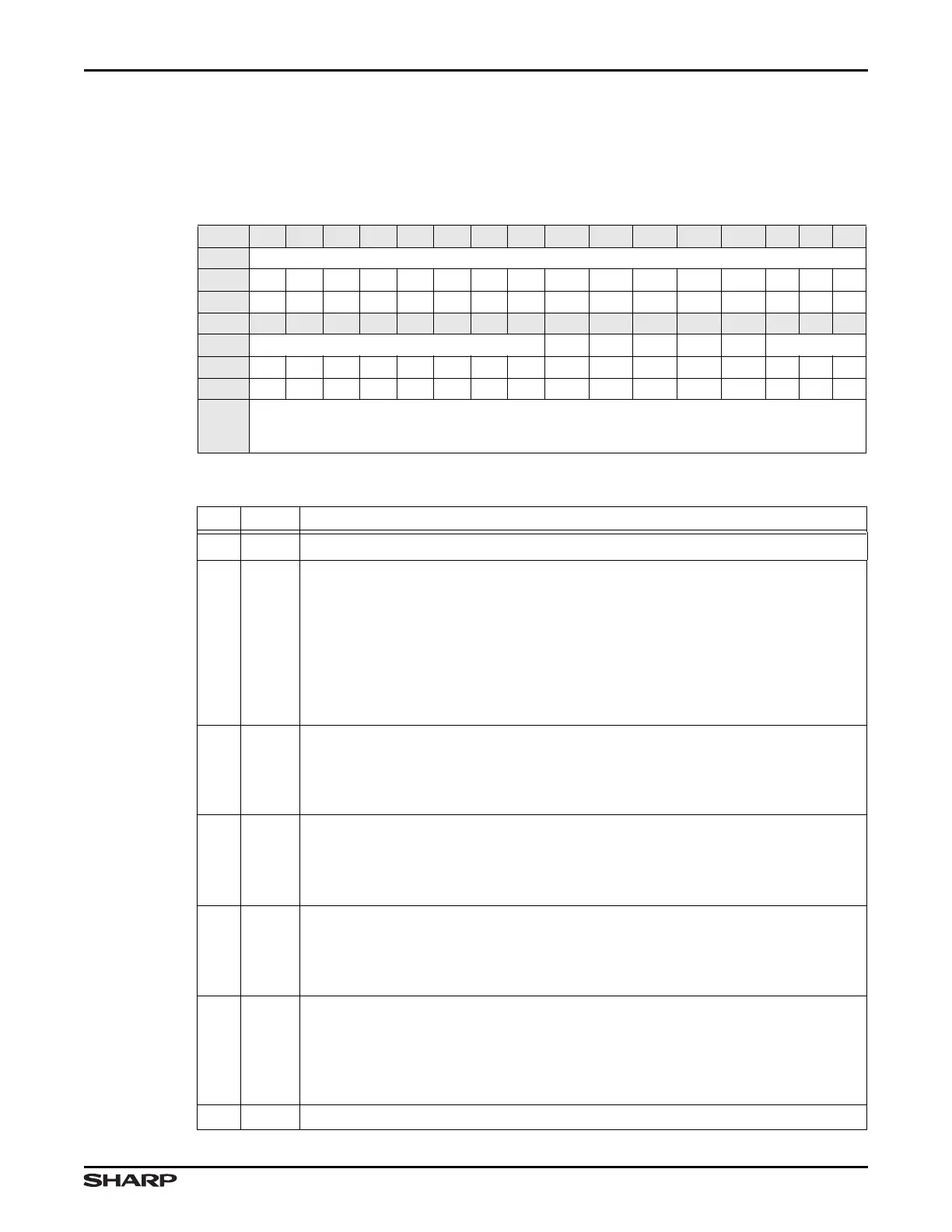

Table 16-11. UARTFR Fields

BIT NAME DESCRIPTION

31:8 ///

Reserved Reading returns 0. Write the reset value.

7TXFE

Transmit FIFO Empty The meaning of this bit depends on the state of the FIFO

Enable bit (UARTLCR_H:FEN). See Section 16.3.2.7.

For UARTLCR_H:FEN = 1 (FIFO enabled)

1 = Transmit FIFO is empty

0 = Transmit FIFO not empty

For UARTLCR_H:FEN = 0 (FIFO disabled)

1 = Transmit Holding Register is empty

0 = Transmit Holding Register not empty

6RXFF

Receive FIFO Full The meaning of this bit depends on the state of the FEN bit

in the UARTLCR_H Register (see Section 16.3.2.7).

FIFO disabled = This bit is set when the Receive Holding Register is full.

FIFO enabled = RXFF bit is set when the receive FIFO is full.

5TXFF

Transmit FIFO Full The meaning of this bit depends on the state of the FEN bit

in the UARTLCR_H Register (see Section 16.3.2.7).

FIFO disabled = This bit is set when the Transmit Holding Register is full.

FIFO enabled = The TXFF bit is set when the transmit FIFO is full.

4RXFE

Receive FIFO Empty The meaning of this bit depends on the state of the FEN

bit in the UARTLCR_H Register (see Section 16.3.2.7).

FIFO disabled = This bit is set when the Receive Holding Register is empty.

FIFO enabled = The RXFE bit is set when the receive FIFO is empty

3BUSY

UART Busy This bit is set as soon as the transmit FIFO becomes

non-empty, regardless of whether the UART is enabled or not.

1 = UART is busy transmitting data. This bit remains set until the complete byte,

including all Stop bits, has been sent from the shift register.

0 = Not busy

2:0 /// Reserved Unpredictable when read; write the reset value.

Loading...

Loading...