Synchronous Serial Port LH79524/LH79525 User’s Guide

14-16 Version 1.0

14.2.2.6 Interrupt Mask Set and Clear Register (IMSC)

IMSC is the Interrupt Mask Set and Clear Register. On a read, this register gives the cur-

rent value of the mask on the relevant interrupt. A write of 1 to the particular bit clears the

mask, enabling the interrupt to be read. A write of 0 sets the corresponding mask.

All bits are cleared to 0 when reset.

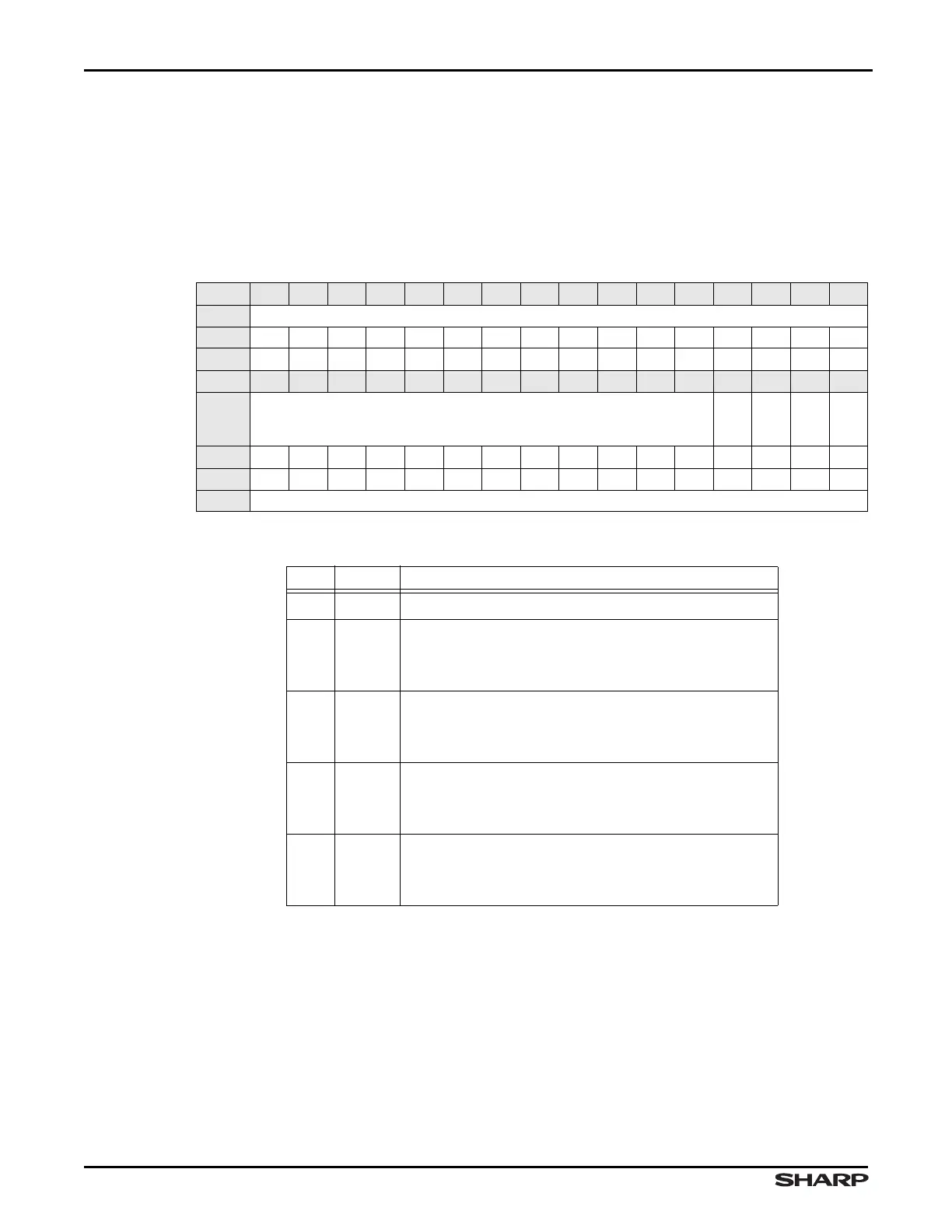

Table 14-13. IMSC Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

TXIM

RXIM

RTIM

RORIM

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW

ADDR 0xFFFC6000 + 0x014

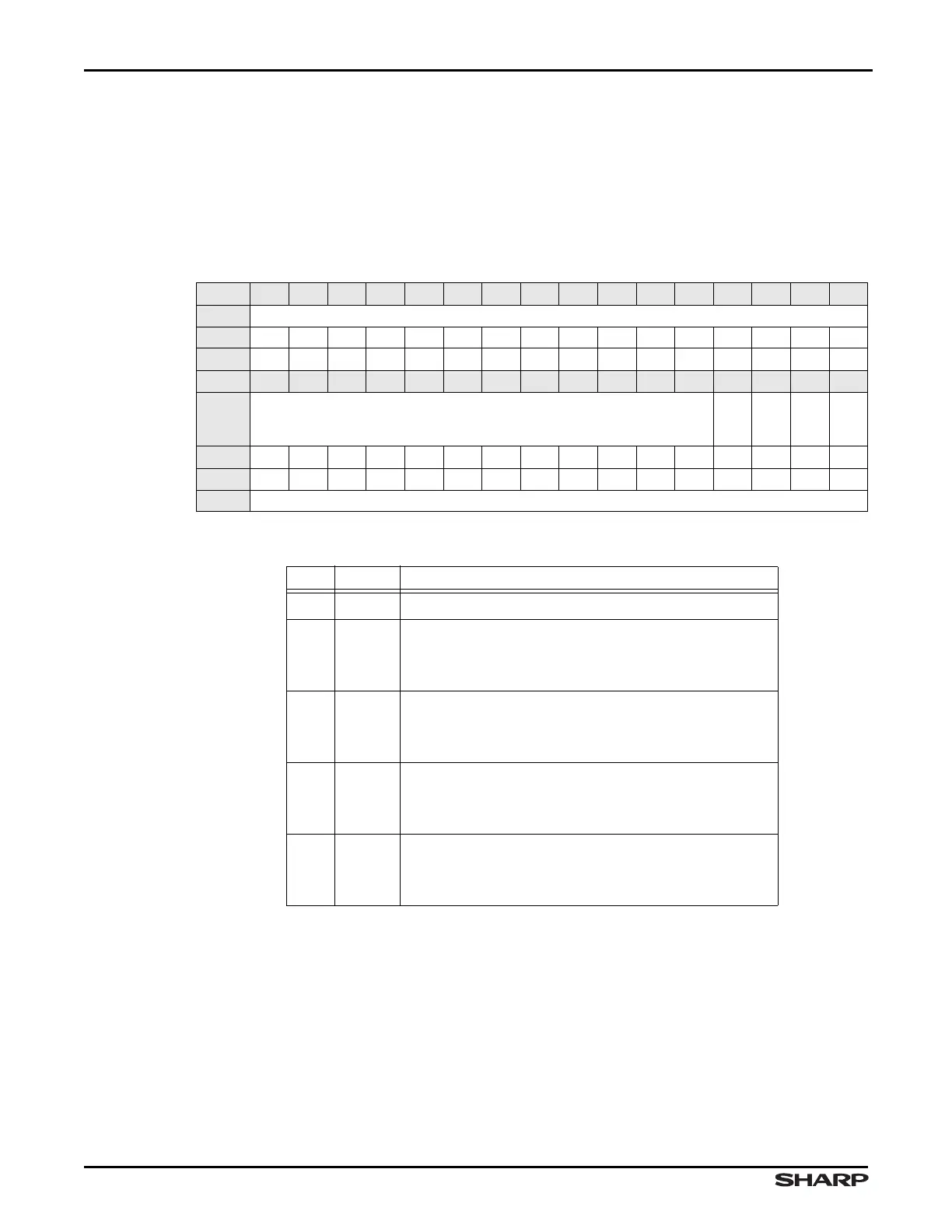

Table 14-14. IMSC Fields

BITS NAME DESCRIPTION

31:4 /// Reserved Reading returns 0. Write the reset value.

3TXIM

Transmit FIFO Interrupt Mask

1 = Interrupt not masked

0 = Interrupt is masked

2RXIM

Receive FIFO Interrupt Mask

1 = Interrupt not masked

0 = Interrupt is masked

1RTIM

Receive Timeout Interrupt Mask

1 = Interrupt not masked

0 = Interrupt is masked

0RORIM

Receive Overrun Interrupt Mask

1 = Interrupt not masked

0 = Interrupt is masked

Loading...

Loading...