Ethernet MAC Controller LH79524/LH79525 User’s Guide

6-2 Version 1.0

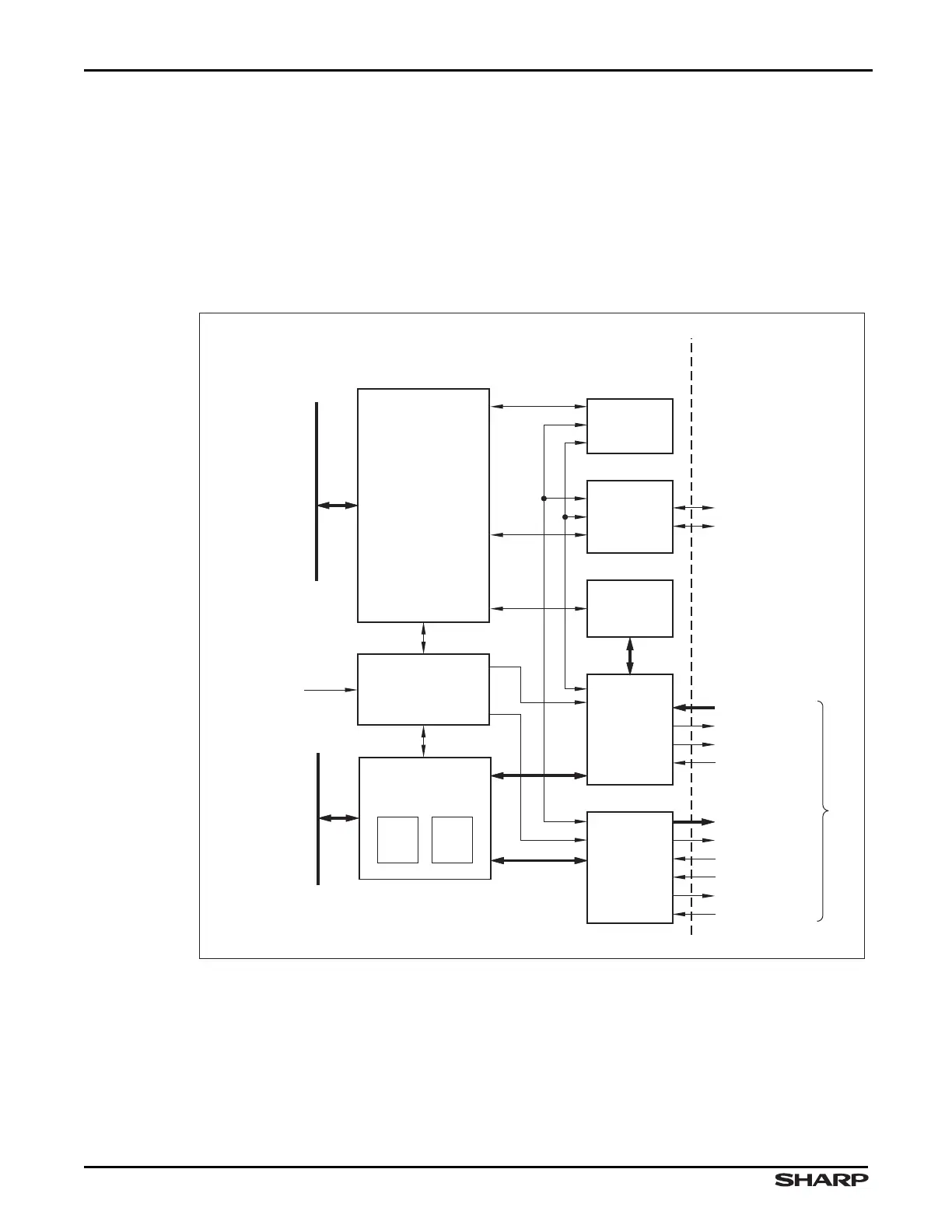

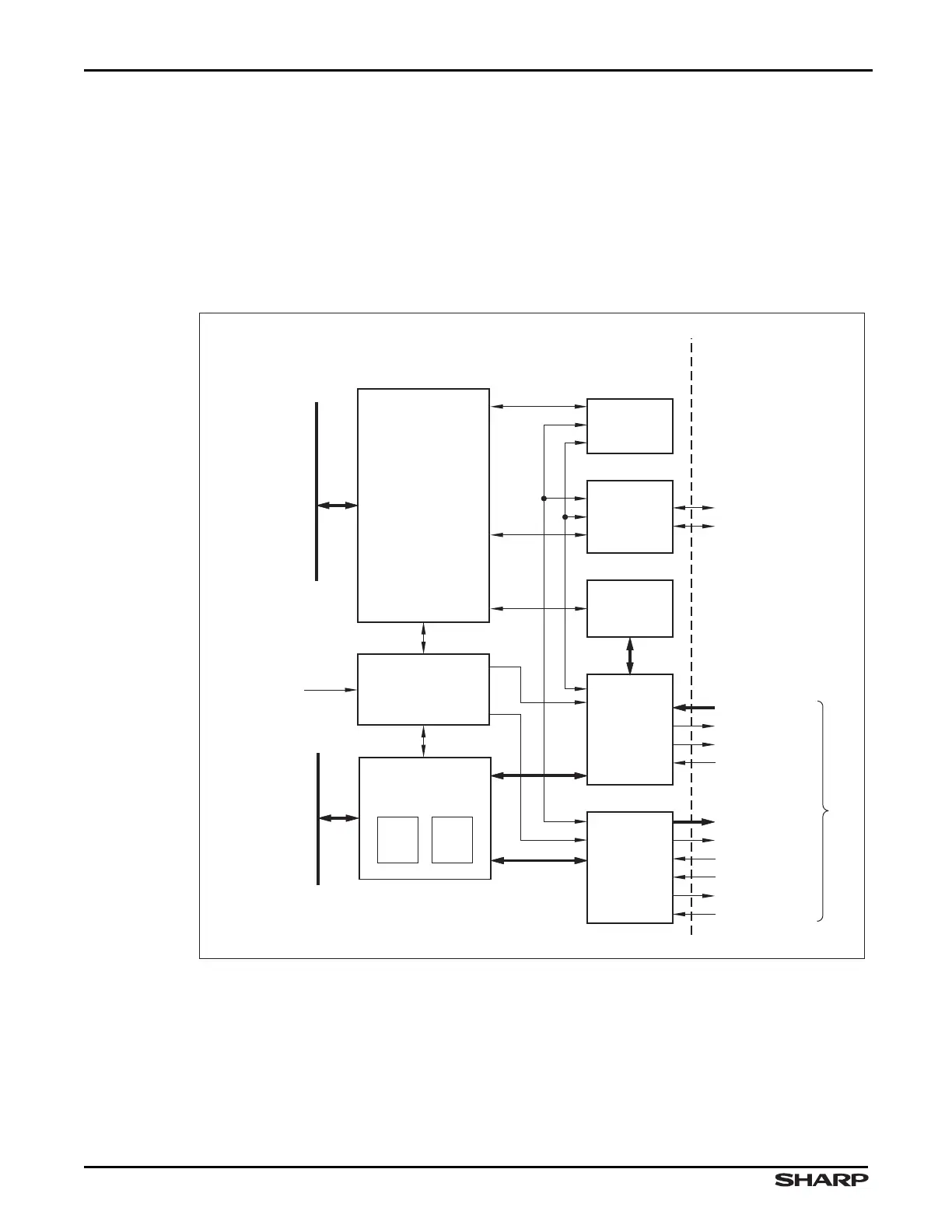

6.1 Theory of Operation

This chapter assumes working knowledge of Ethernet protocol and the IEEE 802.3 spec-

ification. The full specification can be obtained at: http://standards.ieee.org/getieee802/

A simplified block diagram of the EMAC appears in Figure 6-1. It is handy to reference the

block diagram as the different interfaces are described in the succeeding sections. The EMAC

is identical for both the LH79524 and LH79525, and all descriptions in this chapter apply to

both devices. Following the Theory of Operation section is a programming example.

Figure 6-1. EMAC Block Diagram

CONTROL

and

STATUS

REGISTERS

ETHERMDIO

ETHERMDC

ETHERRX[3:0]

ETHERRXER

ETHERRXDV

ETHERRXCLK

ETHERRTX[3:0]

ETHERTXER

ETHERCOL

MII

ETHERCRS

ETHERTXEN

ETHERTXCLK

STATUS

REGISTERS

REGISTER

INTERFACE

ADDRESS

CHECKING

BLOCK

CLOCK

GENERATION

and

SYNCHRONIZATION

DMA

INTERFACE

TX

FIFO

ETHERNET

RECEIVE

BLOCK

ETHERNET

TRANSMIT

BLOCK

INTERNAL TO

THE LH79524/LH79525

EXTERNAL TO

THE LH79524/LH79525

RX

FIFO

ADVANCED HIGH

PERFORMANCE

BUS (AHB)

ADVANCED

PERPHERAL

BUS (APB)

HCLK

LH79525-6

Loading...

Loading...