UARTs LH79524/LH79525 User’s Guide

16-8 Version 1.0

16.3.2 Register Definitions

16.3.2.1 Data Register (UARTDR)

UARTDR is the Data Register for words that are to be transmitted or have been received

over the serial interface. Writing to this register initiates transmission from the UART.

• If the FIFOs are enabled, data written to this location is pushed to the transmit FIFO.

• If the FIFOs are not enabled, data is stored in the Transmitter Holding Register (THOR),

the bottom word of the transmit FIFO.

A read of this register pops the first word from the receive FIFO. This word consists of the

received character and the associated error bits.

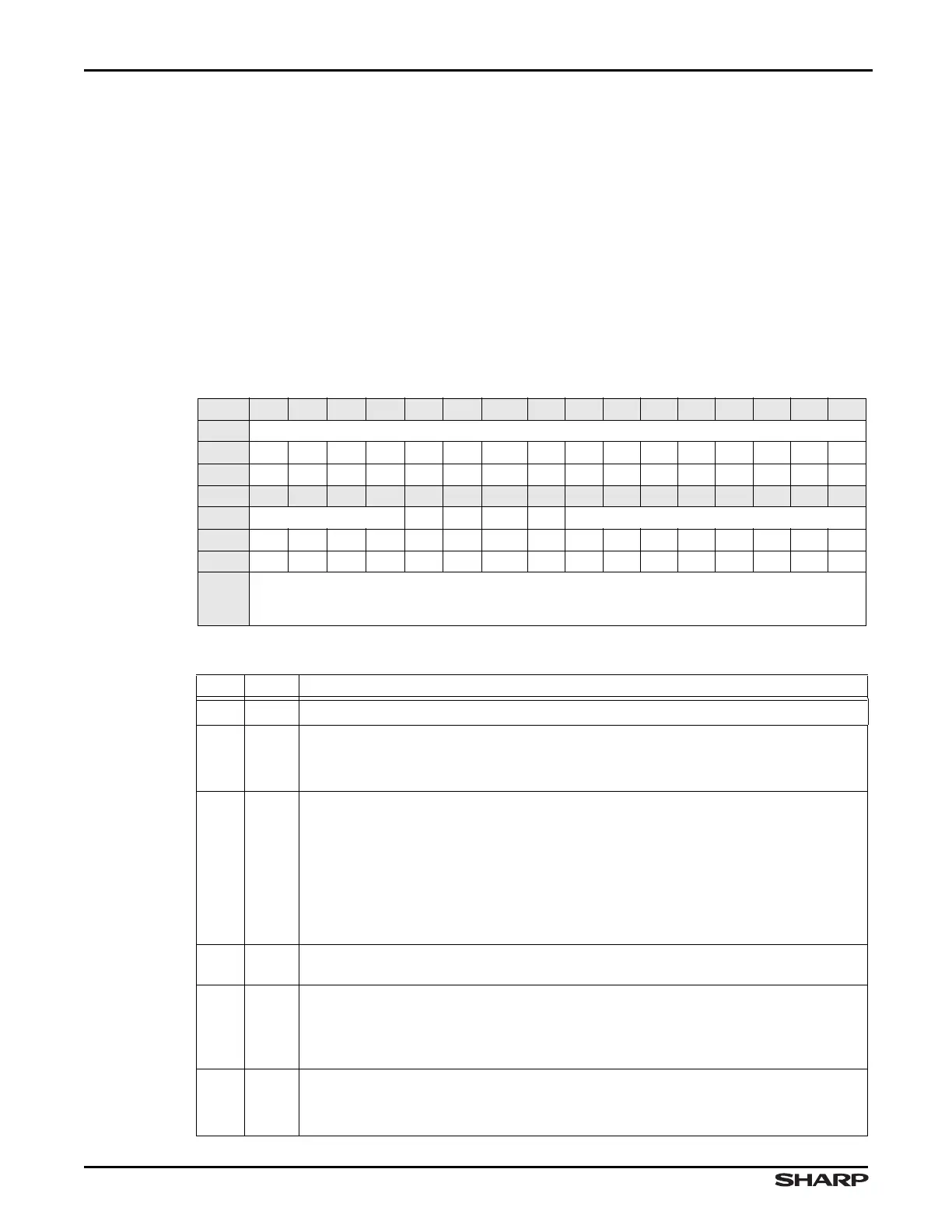

Table 16-3. UARTDR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 000000 0 000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// OE BE PEAR FE DATA

RESET 000000 0 000000000

RW RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR

UART 0: 0xFFFC0000 + 0x000

UART 1: 0xFFFC1000 + 0x000

UART 2: 0xFFFC2000 + 0x000

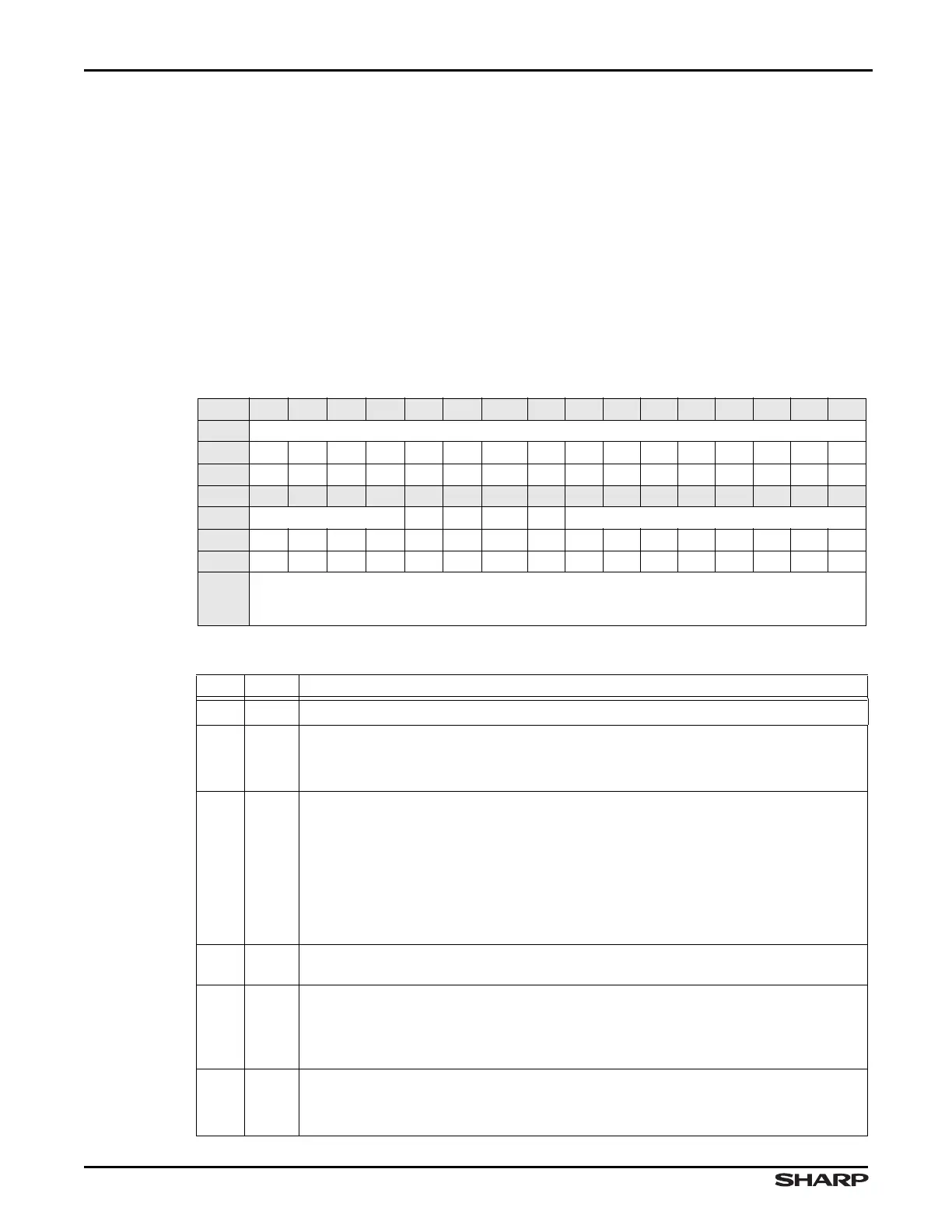

Table 16-4. UARTDR Fields

BIT NAME DESCRIPTION

31:12 /// Reserved Reading returns 0. Write the reset value.

11 OE

Receive FIFO Full/Empty This bit indicates an overrun condition.

1 = Data is received and the receive FIFO is already full

0 = There is an empty space in the FIFO and a new character can be written

10 BE

Break Error This bit indicates a Break has occurred. It is cleared to 0 after a Write to the

UARTECR Register. In FIFO Mode, this error is associated with the character at the top of

the FIFO. When a break occurs, only one 0 character is loaded into the FIFO. The next char-

acter is only enabled after the receive data input goes to a 1 (Idle state) and the next valid

Start bit is received.

1 = A Break condition was detected, indicating that the received data input was held LOW

for longer than a full-word transmission time (defined as Start, data, parity and Stop bits)

0 = No Break

9 PEAR

Parity Error/Address Received See Table 16-5. In FIFO mode, this error is associated

with the character at the top of the FIFO.

8FE

Framing Error This bit indicates that a Framing Error has occurred. In FIFO Mode, this

error is associated with the character at the top of the FIFO.

1 = The received character did not have a valid Stop bit (a valid Stop bit is 1)

0 = No Framing Error

7:0 DATA

Receive/Transmit Data Character This field contains the receive or transmit data.

Read = Receive data character

Write = Transmit data character

Loading...

Loading...