LH79524/LH79525 User’s Guide Synchronous Serial Port

Version 1.0 14-13

14.2.2.3 Data Register – Receive/Transmit FIFO Register (DR)

DR is the 16-bit-wide Receive/Transmit FIFO register.

• When DR is read, the entry in the receive FIFO (pointed to by the current FIFO read

pointer) is accessed. As data values are removed by the SSP's receive logic from the

incoming data frame, they are placed into the entry in the receive FIFO (pointed to by

the current FIFO write pointer).

• When DR is written to, the entry in the transmit FIFO (pointed to by the write pointer), is

written with the DR data. Data values are removed from the transmit FIFO one value at

a time by the transmit logic. Each value is loaded into the transmit serial shifter, then

serially shifted out onto the SSPTX pin at the programmed bit rate.

When a data size of less than 16 bits is selected, software must right-justify data written to

the transmit FIFO. The transmit logic ignores the unused bits. Received data less than 16

bits is automatically right-justified in the 16-bit wide receive buffer. Software should ignore

(by masking) the receive buffer upper unused bits.

When the SSP is programmed for National Microwire frame format in master mode, the

default size for transmit data is eight bits (the most-significant byte is ignored). The receive

data size is controlled by software. When the SSP is the slave device, it will receive 8 bits

of control data and transmit 4 to 16 bits of data. The transmit FIFO and the receive FIFO

are not cleared, even when the SSE bit in Control Register 1 is set to 0 (refer to

Section 14.2.2.2). This allows the software to fill the transmit FIFO before enabling the SSP.

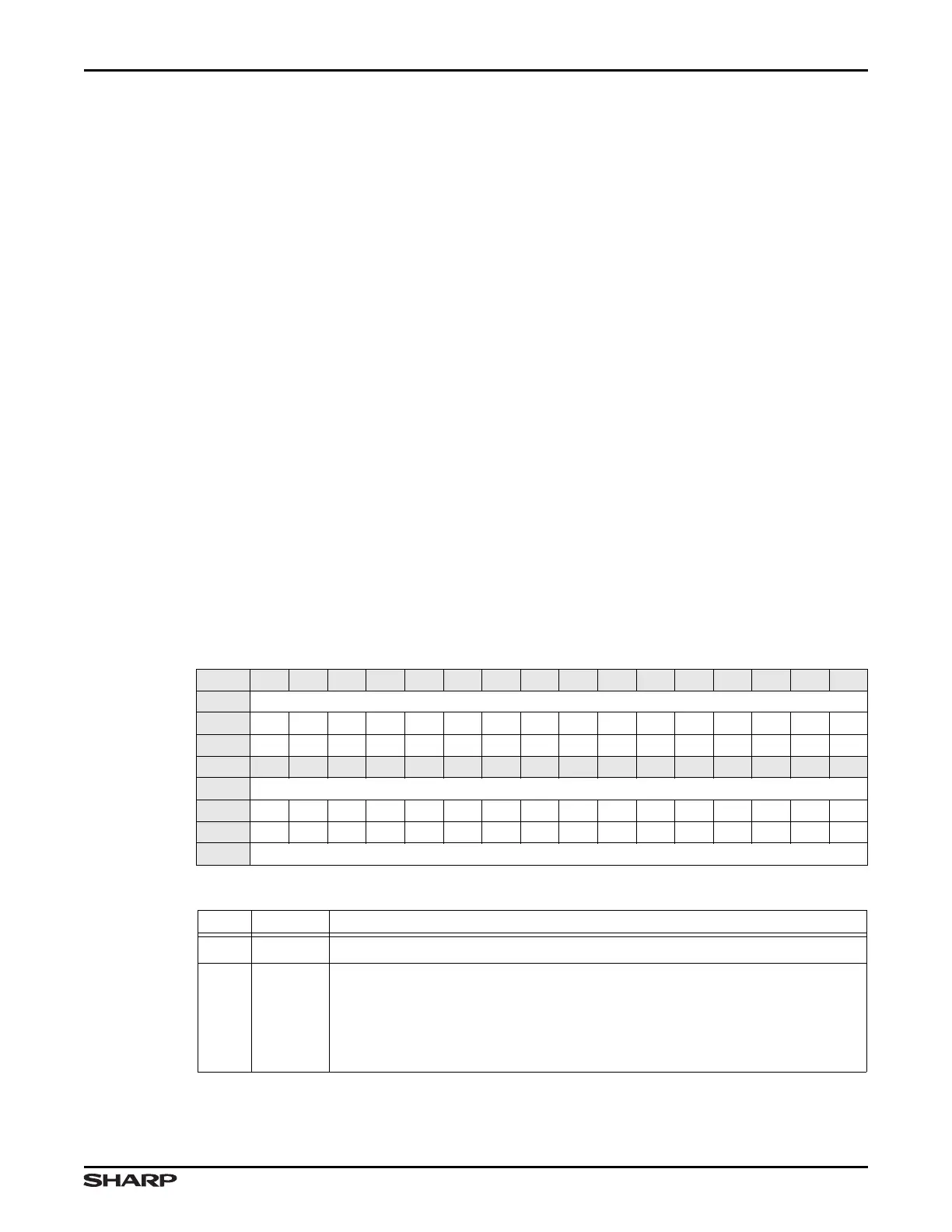

Table 14-7. DR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD DATA

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC6000 + 0x008

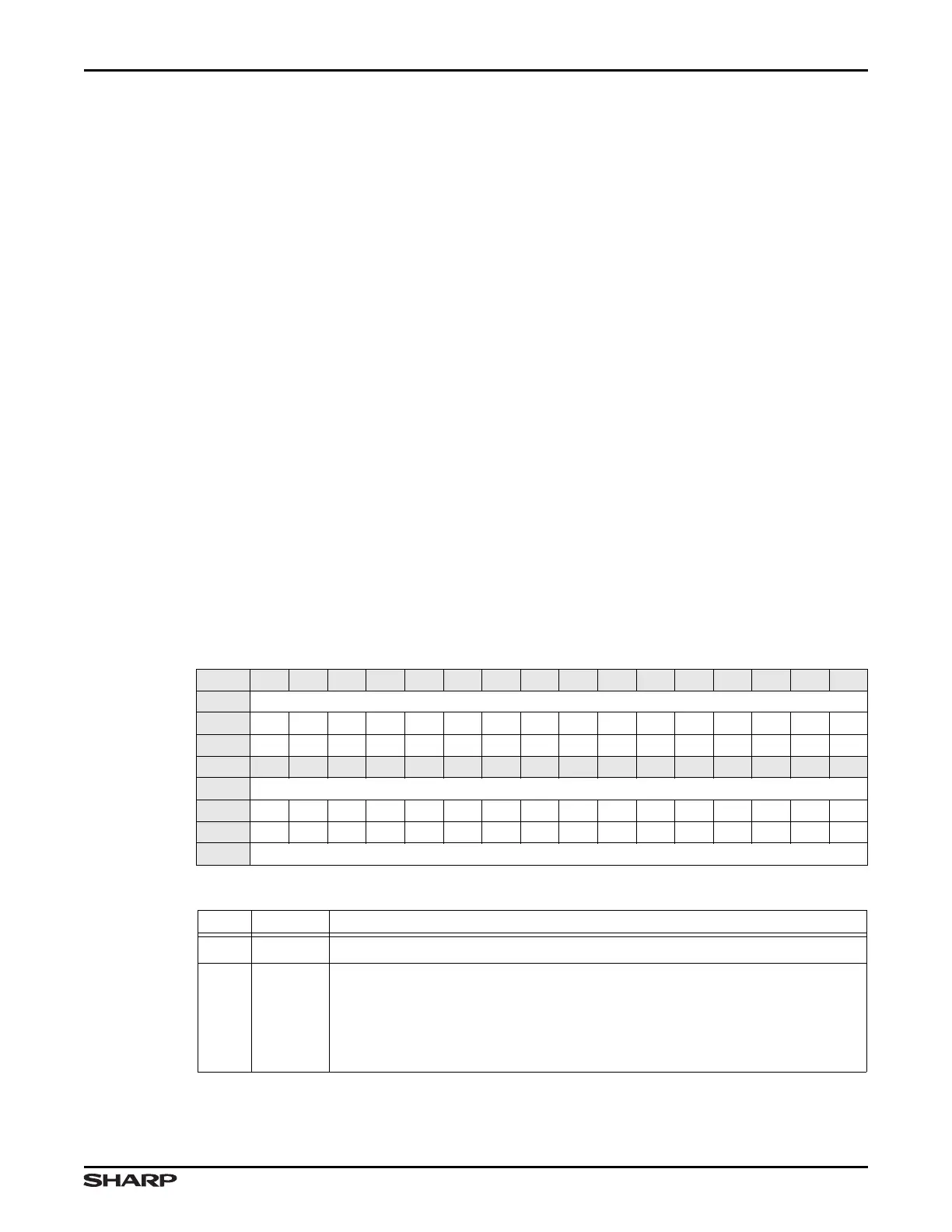

Table 14-8. DR Fields

BITS NAME DESCRIPTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:0 DATA

Transmit/Receive FIFO Right-justify data when the SSP is programmed for

a data size that is smaller than 16 bits. Unused bits at the top are ignored by

transmit logic. The receive logic automatically right-justifies.

Read = Receive FIFO top entry

Write = Transmit FIFO top entry

Loading...

Loading...