LH79524/LH79525 User’s Guide Timers

Version 1.0 15-17

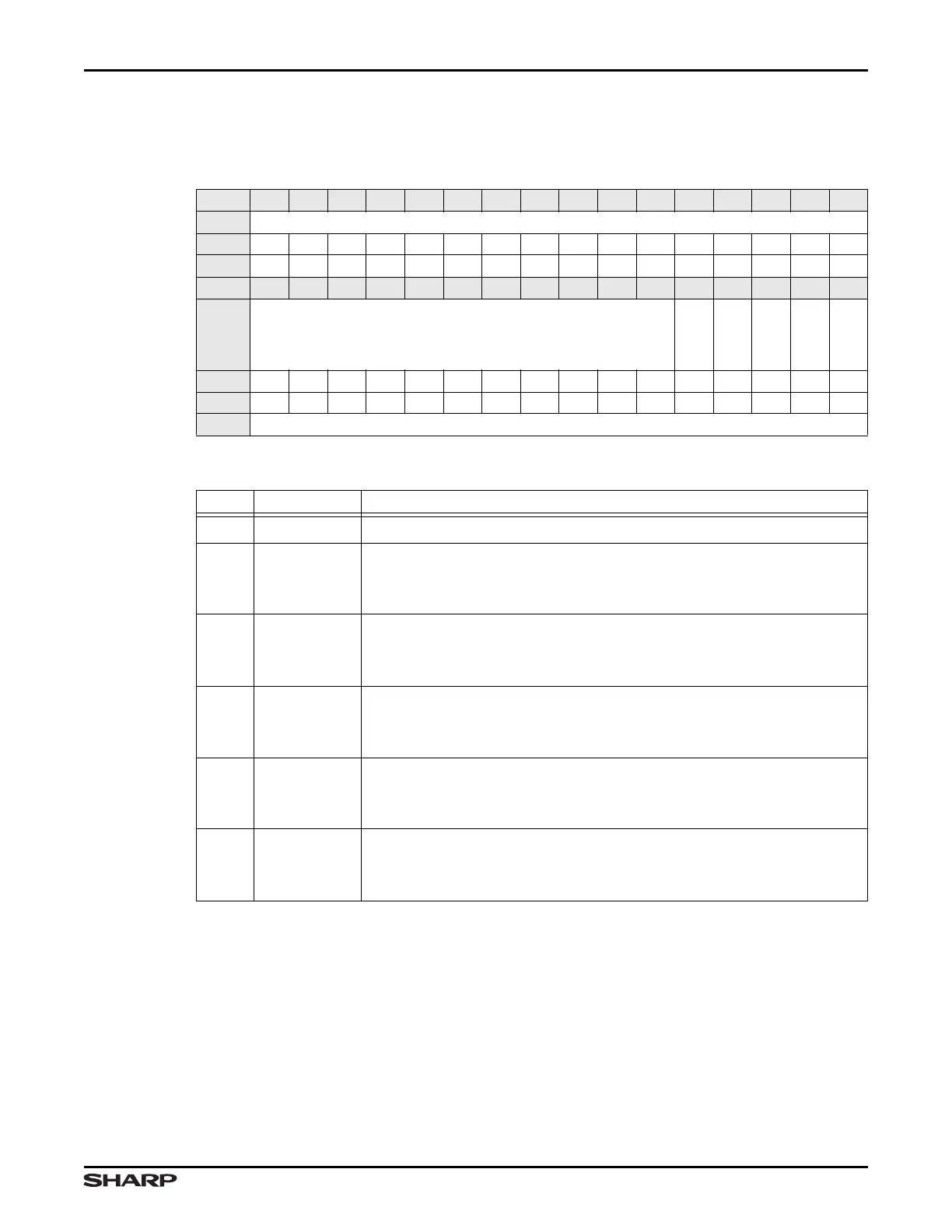

15.2.2.9 Timer 1 Interrupt Control Register (INTEN1)

This register allows software to enable and disable individual interrupts as needed.

Table 15-20. INTEN1 Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

CAPB_EN

CAPA_EN

CMP1_EN

CMP0_EN

OVF_EN

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW RW

ADDR 0xFFFC4000 + 0x34

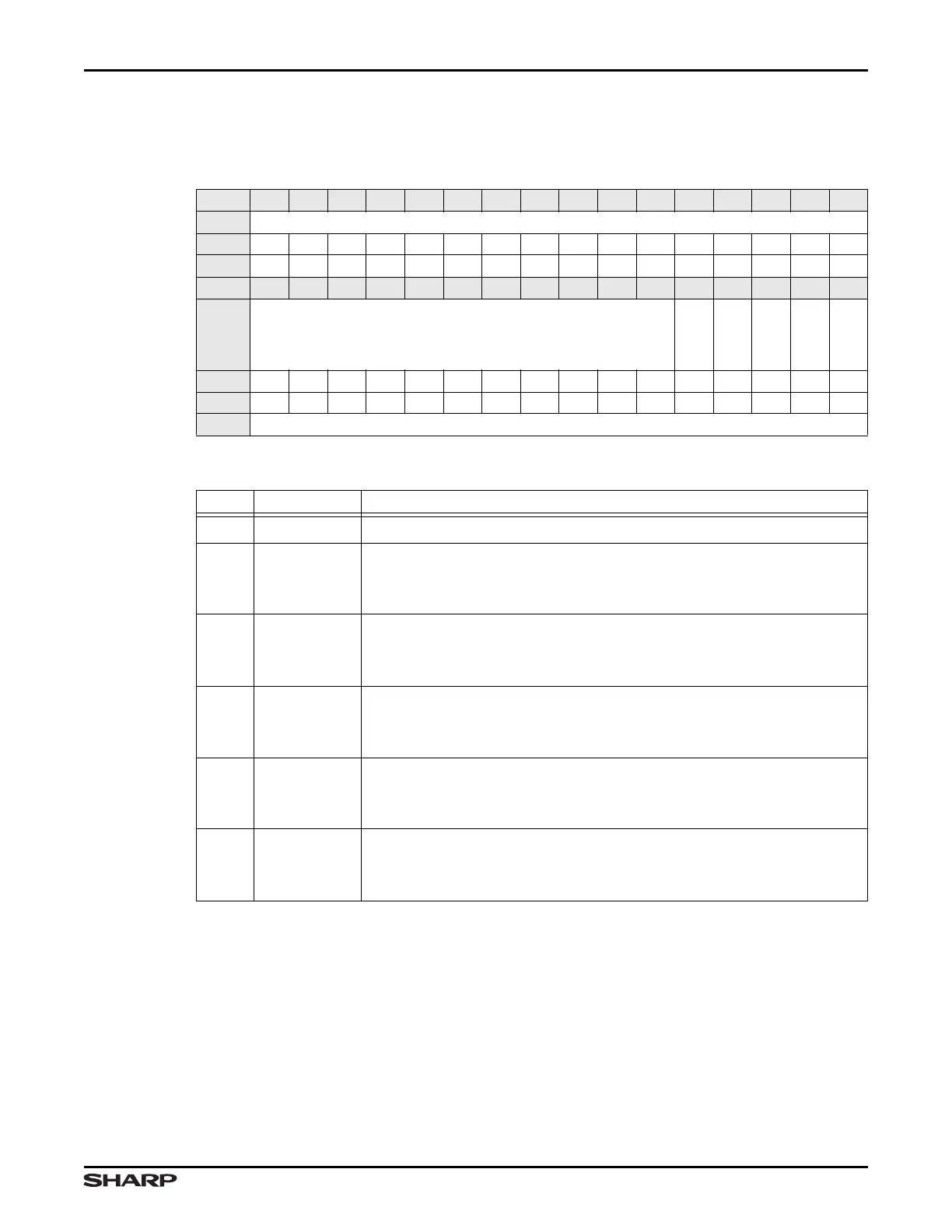

Table 15-21. INTEN1 Register Definitions

BITS NAME DESCRIPTION

31:5 ///

Reserved Reading this field returns 0. Write the reset value.

4 CAPB_EN

Timer 1 Interrupt Enable During Capture 1 Operation

1 = Interrupt enabled for capture B

0 = Interrupt disabled for capture B

3 CAPA_EN

Timer 1 Interrupt Enable During Capture A Operation

1 = Interrupt enabled for capture A

0 = Interrupt disabled for capture A

2CMP1_EN

Timer 1 Interrupt Enable Upon Compare 1

1 = Interrupt enabled for compare 1

0 = Interrupt disabled for compare 1

1 CMP0_EN

Timer 1 Interrupt Enable Upon Compare 0

1 = Interrupt enabled for compare 0

0 = Interrupt disabled for compare 0

0OVF_EN

Timer 1 Interrupt Overflow Enable

1 = Interrupt enabled for counter overflows

0 = Interrupt disabled for counter overflows

Loading...

Loading...