External Memory Controller LH79524/LH79525 User’s Guide

7-54 Version 1.0

7.5.2.22 Static Memory Write Enable Delay Registers (SWAITWENx)

The Static Memory Write Enable Delay Registers allow programming a delay between

Address Valid and the assertion of nWE (nBLEx). See Section 7.2.4.1.2 for a complete

description of programming these registers.

Wait states behave slightly differently for Write transactions than for Reads. Instead

of the length of the Write cycle (tWC) being the sum of the valued programmed into the

SWAITWENx and SWAITWRx registers, it has the following relationship (with ‘A’ being

SWAITWENx, ‘B’ being SWAITWRx, and ‘C’ being the address hold time):

tWC = tA0 + tB0 + tB1 ... tBn + C, where the length of each term is one HCLK period, and

‘n’ is the value programmed in the respective register.

The minimum value for the equation is tWC = tA0 + tB0 + C, and is therefore the zero wait

state timing.

Note that additional ‘A’ terms (delaying the assertion of nWE or nBLEx) do not add wait

states. This also requires that: SWAITWRx

≥ SWAITWENx.

These registers must only be modified during system initialization, or when there are

no current or outstanding transactions. Software can ensure that there are no current or

outstanding transactions by waiting until the memory controller is idle, then entering

Low-Power Mode (CONTROL:MODE = 1), or Disable Mode (CONTROL:ENABLE = 0).

When in these two modes, external memory access is not allowed, ensuring that

changing parameters will not corrupt external data. Low-Power Mode automatically

refreshes SDRAM; Disable Mode requires commanding the SDRAM to Self Refresh

(DYNMCTRL:SR = 1) prior to entering Disable.

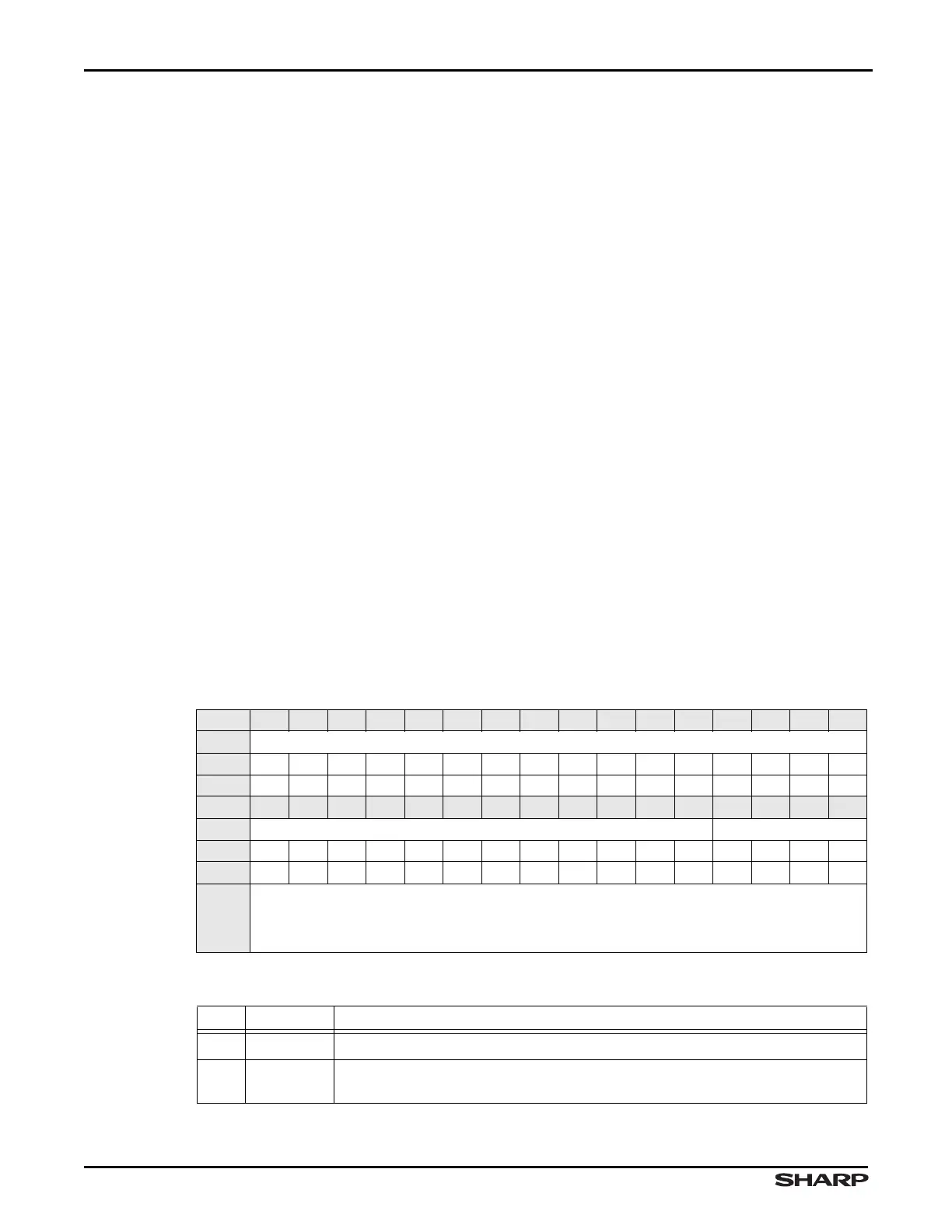

Table 7-54. SWAITWENx Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// WAITWEN

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW

ADDR

0xFFFF1000 + 0x204 for SWAITWEN0

0xFFFF1000 + 0x224 for SWAITWEN1

0xFFFF1000 + 0x244 for SWAITWEN2

0xFFFF1000 + 0x264 for SWAITWEN3

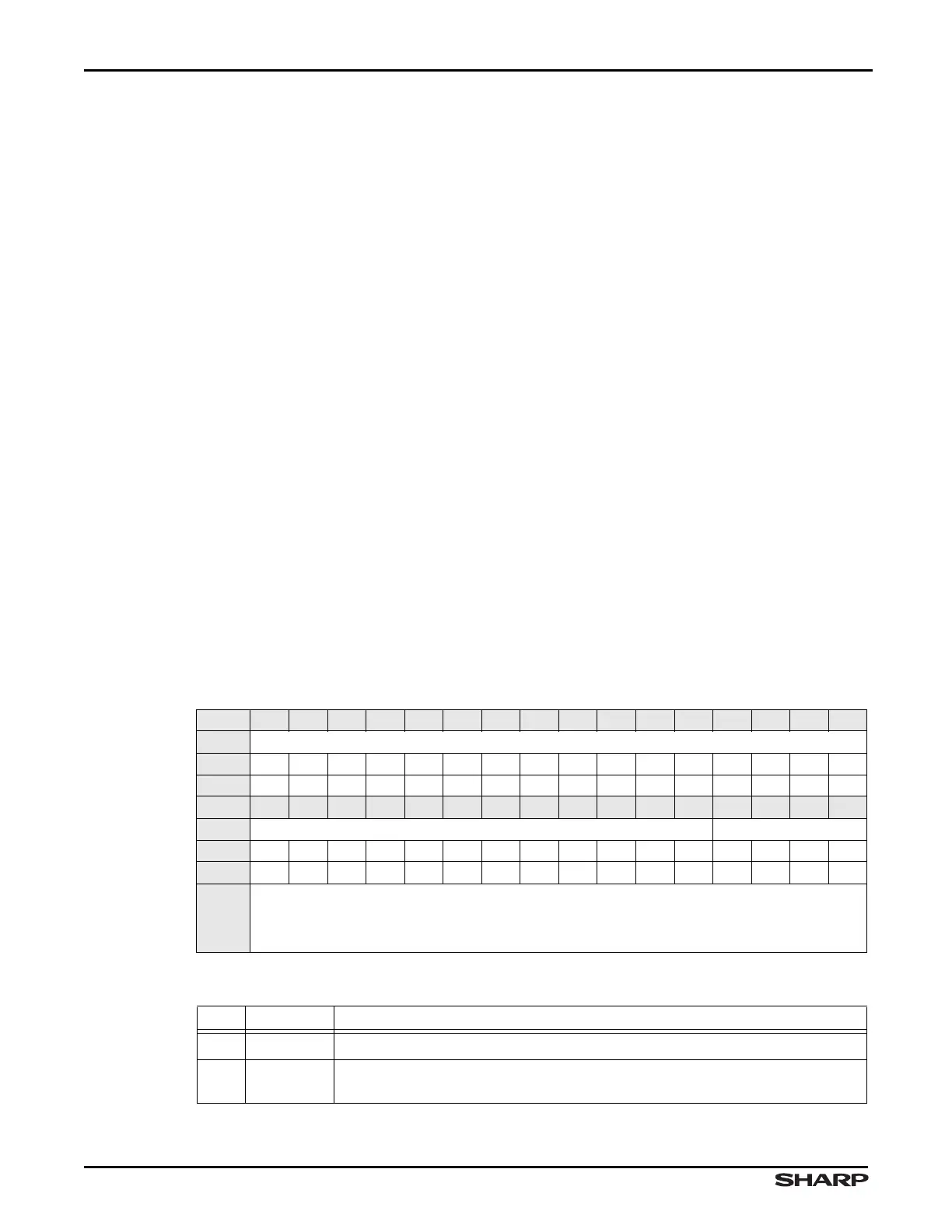

Table 7-55. SWAITWENx Fields

BITS NAME FUNCTION

31:4 /// Reserved Reading returns 0. Write the reset value.

3:0 WAITWEN

Wait Write Enable Program the delay from assertion of nCSx to the asser-

tion of nWE (nBLEx). See Section 7.2.4.1.2 for timing examples.

Loading...

Loading...