LH79524/LH79525 User’s Guide UARTs

Version 1.0 16-19

16.3.2.9 Interrupt FIFO Level Select Register (UARTIFLS)

UARTIFLS is the Interrupt FIFO Level Select Register. The UARTIFLS Register defines

the FIFO level at which interrupts are generated to request service for the receive and

transmit FIFOs. The interrupts are generated based on a transition through a level rather

than being based on the level; that is, the design is such that the interrupts are generated

when the fill level progresses through the trigger level. The bits are reset so that the trigger

level is when the FIFOs are at the half-way mark.

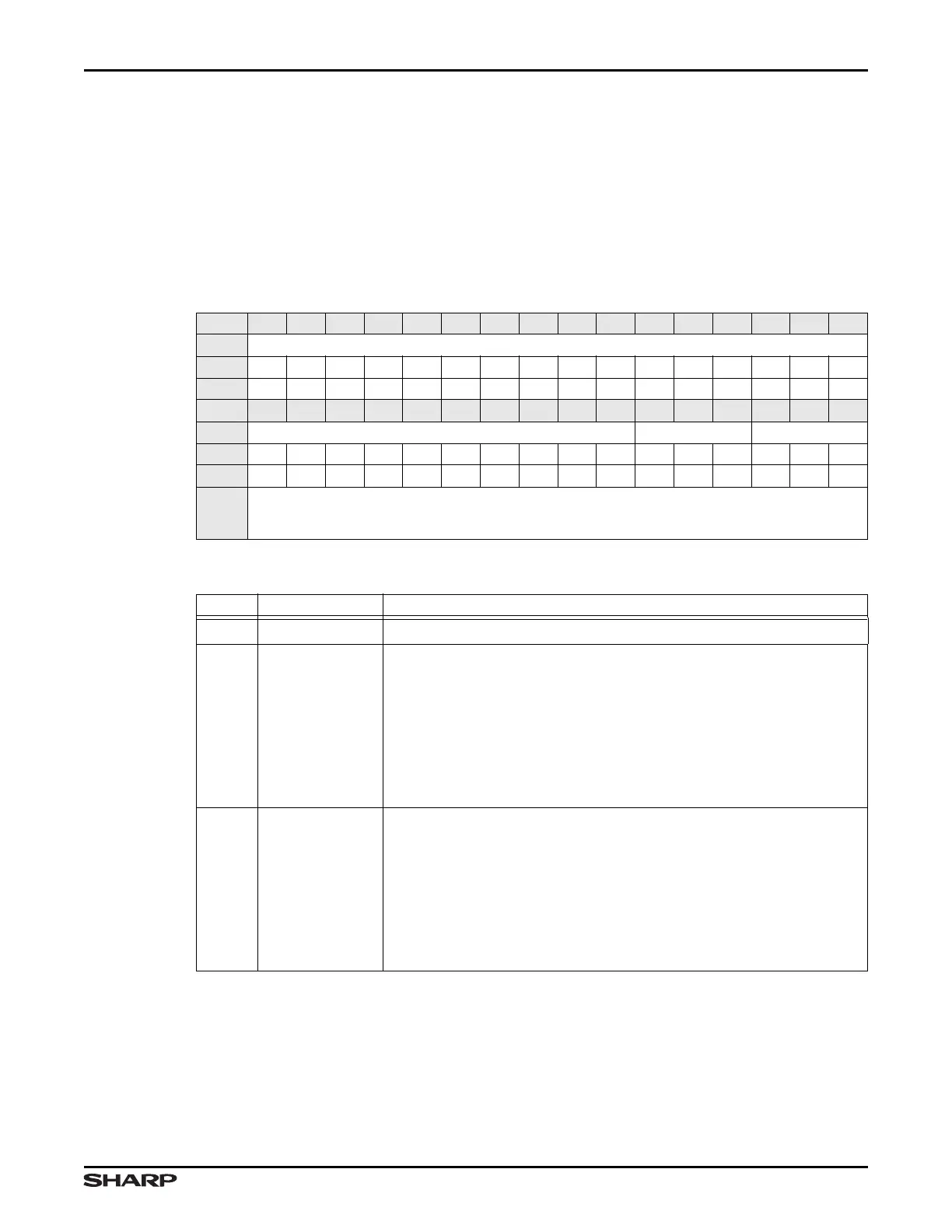

Table 16-24. UARTIFLS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// RXIFLSEL TXIFLSEL

RESET 0000000000010010

RW RO RO RO RO RO RO RO RO RO RO RW RW RW RW RW RW

ADDR

UART 0: 0xFFFC0000 + 0x034

UART 1: 0xFFFC1000 + 0x034

UART 2: 0xFFFC2000 + 0x034

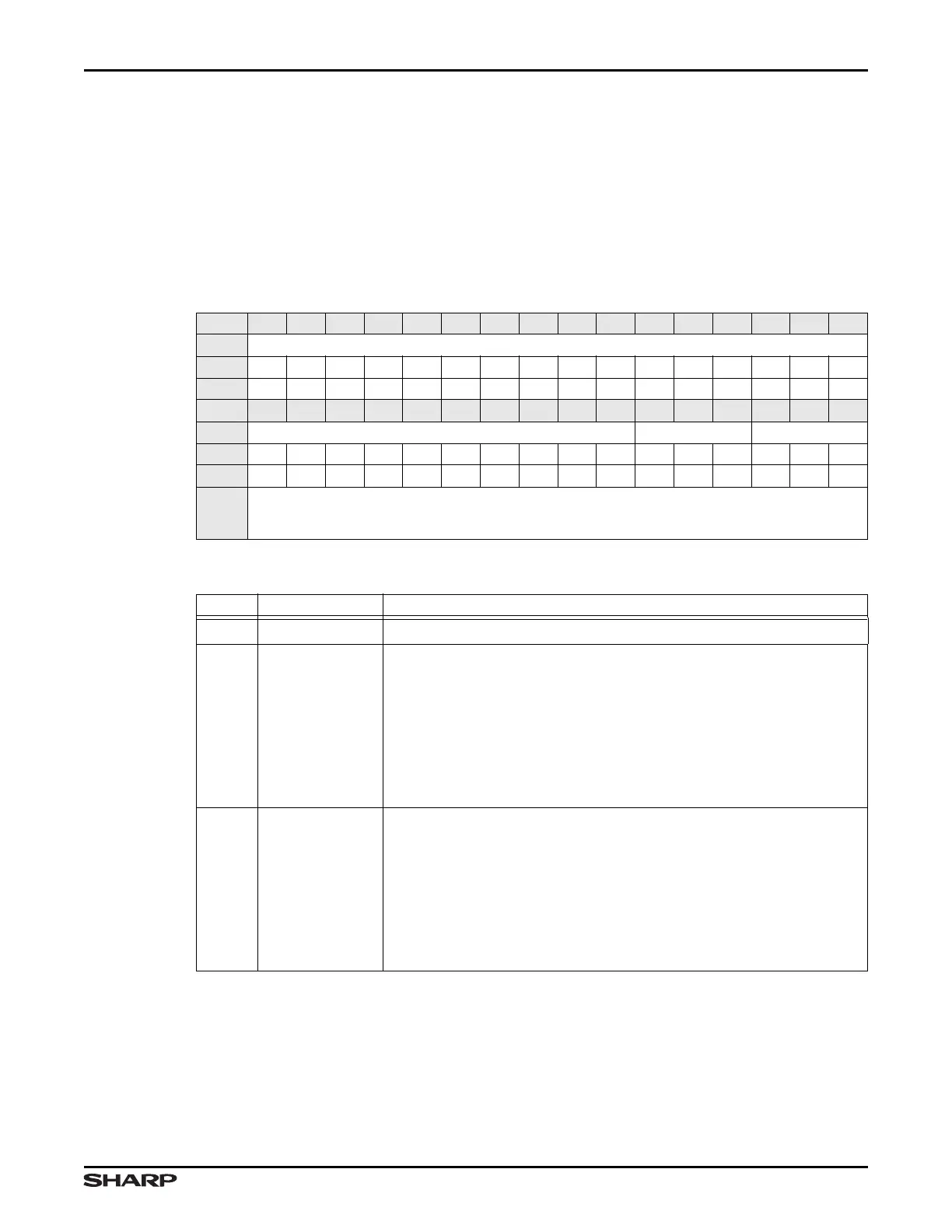

Table 16-25. UARTIFLS Fields

BIT NAME DESCRIPTION

31:6 /// Reserved Reading returns 0. Write the reset value.

5:3 RXIFLSEL

Trigger Points for the Receive Interrupt

000 = Receive FIFO becomes

≥ 1/8 full

001 = Receive FIFO becomes

≥ 1/4 full

010 = Receive FIFO becomes

≥ 1/2 full

011 = Receive FIFO becomes

≥ 3/4 full

100 = Receive FIFO becomes

≥ 7/8 full

101 = Receive FIFO becomes full

110:111 = Invalid

2:0 TXIFLSEL

Trigger Points for the Transmit Interrupt

000 = Transmit FIFO becomes

≤ 1/8 full

001 = Transmit FIFO becomes

≤ 1/4 full

010 = Transmit FIFO becomes

≤ 1/2 full

011 = Transmit FIFO becomes

≤ 3/4 full

100 = Transmit FIFO becomes

≤ 7/8 full

101 = Transmit FIFO becomes empty

110:111 = Invalid

Loading...

Loading...