Vectored Interrupt Controller LH79524/LH79525 User’s Guide

18-6 Version 1.0

18.2.2 Register Descriptions

This section describes the bit fields, reset values, and uses of the registers. For simplicity,

all of the following register tables indicate the default base addresses.

18.2.2.1 IRQ Status Register (IRQSTATUS)

This Read Only register provides the status of all interrupts [31:0] after IRQ masking. Bits

[31:0] correspond to the interrupt number in Table 18-1.

0x220 VECTCTRL8 Vector Control 8 Register

0x224 VECTCTRL9 Vector Control 9 Register

0x228 VECTCTR10 Vector Control 10 Register

0x22C VECTCTRL11 Vector Control 11 Register

0x230 VECTCTRL12 Vector Control 12 Register

0x234 VECTCTRL13 Vector Control 13 Register

0x238 VECTCTRL14 Vector Control 14 Register

0x23C VECTCTRL15 Vector Control 15 Register

0x240 - 0x308 /// Reserved — Do not access

0x30C ITOP Interrupt Test Output Register

0x310 /// Reserved — Do not access

Table 18-2. VIC Register Summary (Cont’d)

ADDRESS OFFSET NAME DESCRIPTION

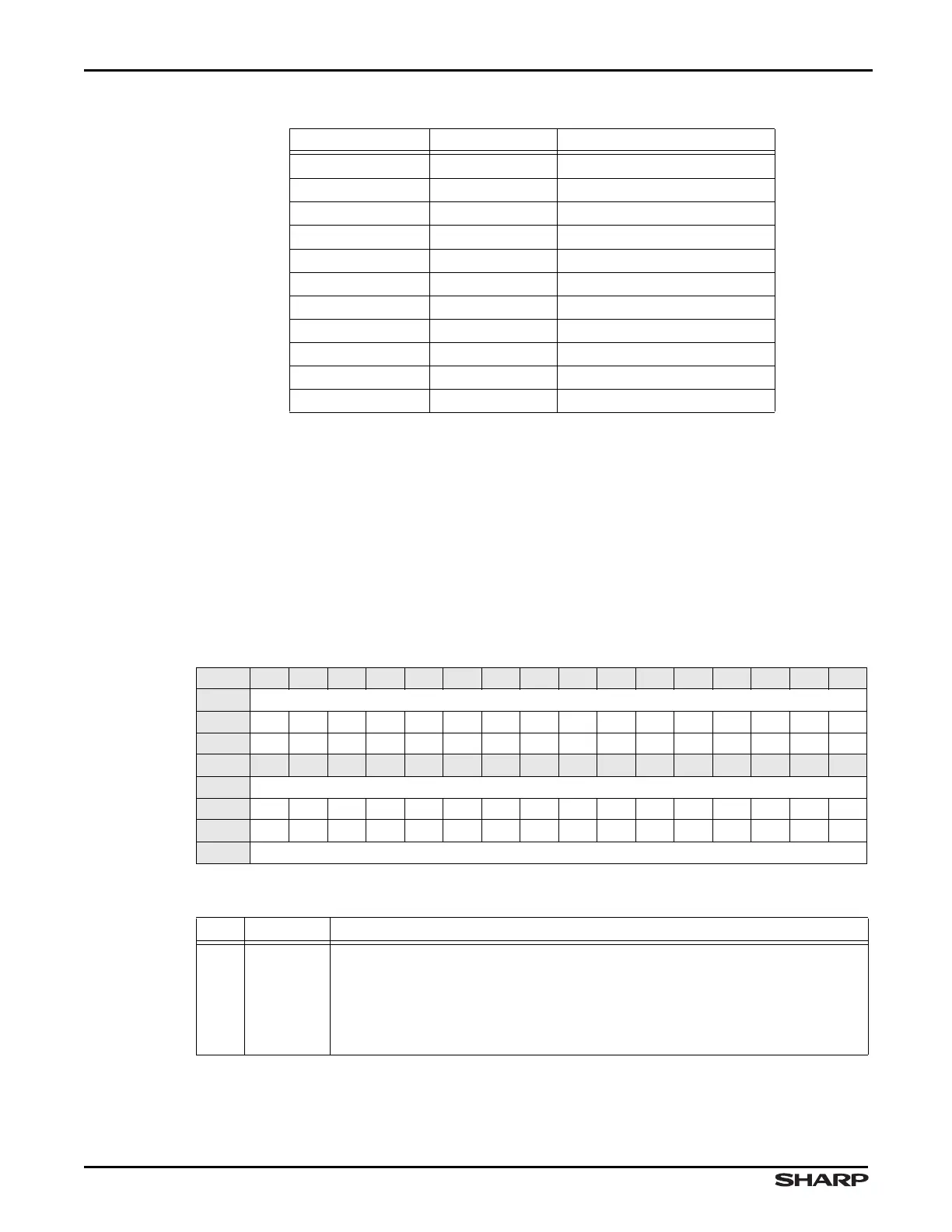

Table 18-3. IRQSTATUS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD IRQStatus

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD IRQStatus

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR 0xFFFFF000 + 0x000

Table 18-4. IRQSTATUS Fields

BITS NAME DESCRIPTION

31:0 IRQStatus

Interrupt Status After Masking Shows the status of the interrupts after

masking by the INTENABLE and INTSELECT Registers.

For each bit:

1 = Interrupt is active and generates an IRQ exception to the ARM7 core

0 = Interrupt is not active

Loading...

Loading...