I/O Configuration LH79524/LH79525 User’s Guide

11-44 Version 1.0

11.2.2.30 Multiplexing Control 22 Register (MUXCTL22)

The MUXCTL22 Register allows software to configure a number of LH79524/LH79525 pins.

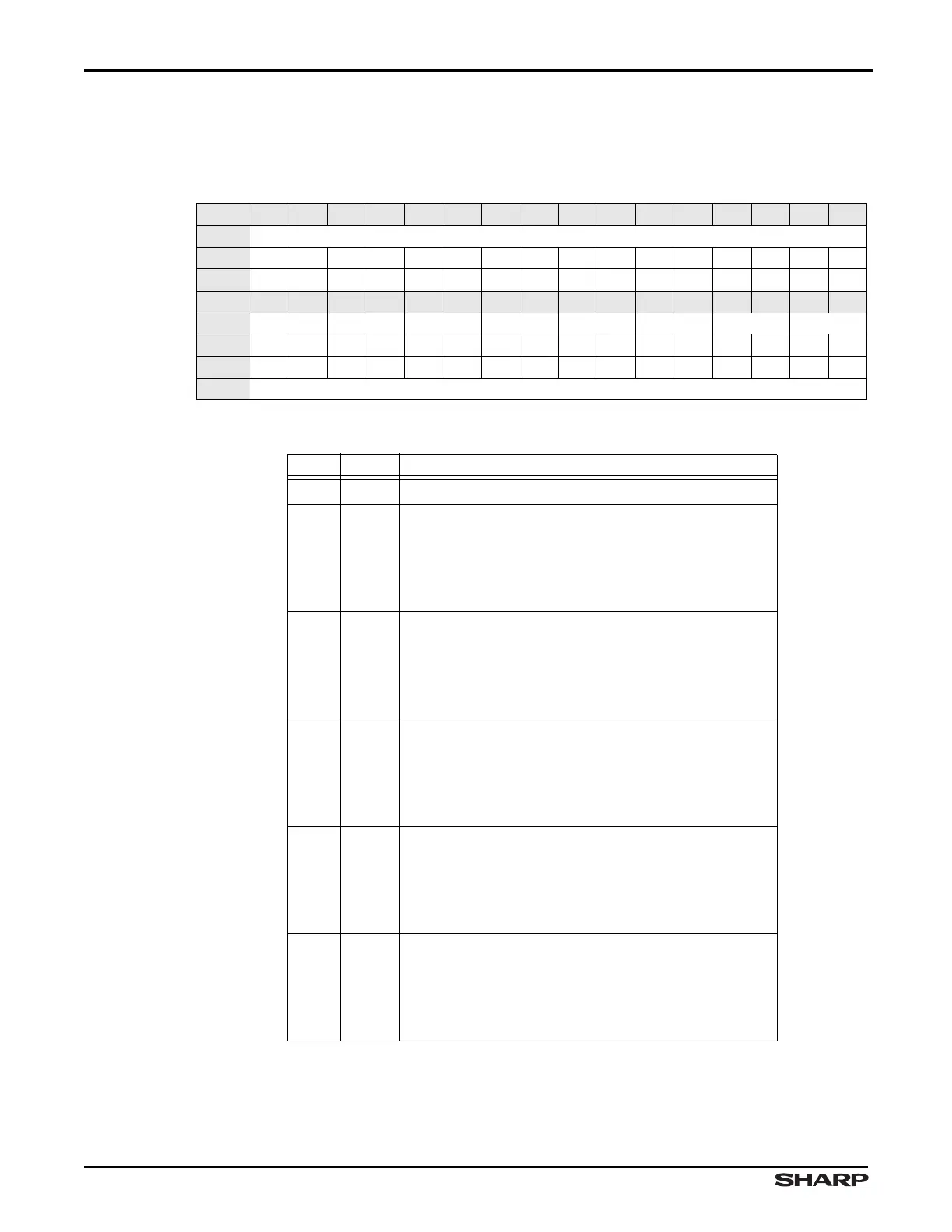

Table 11-60. MUXCTL22 Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD PF1 PF0 PG7 PG6 PG5 PG4 PG3 PG2

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFE5000 + 0xA8

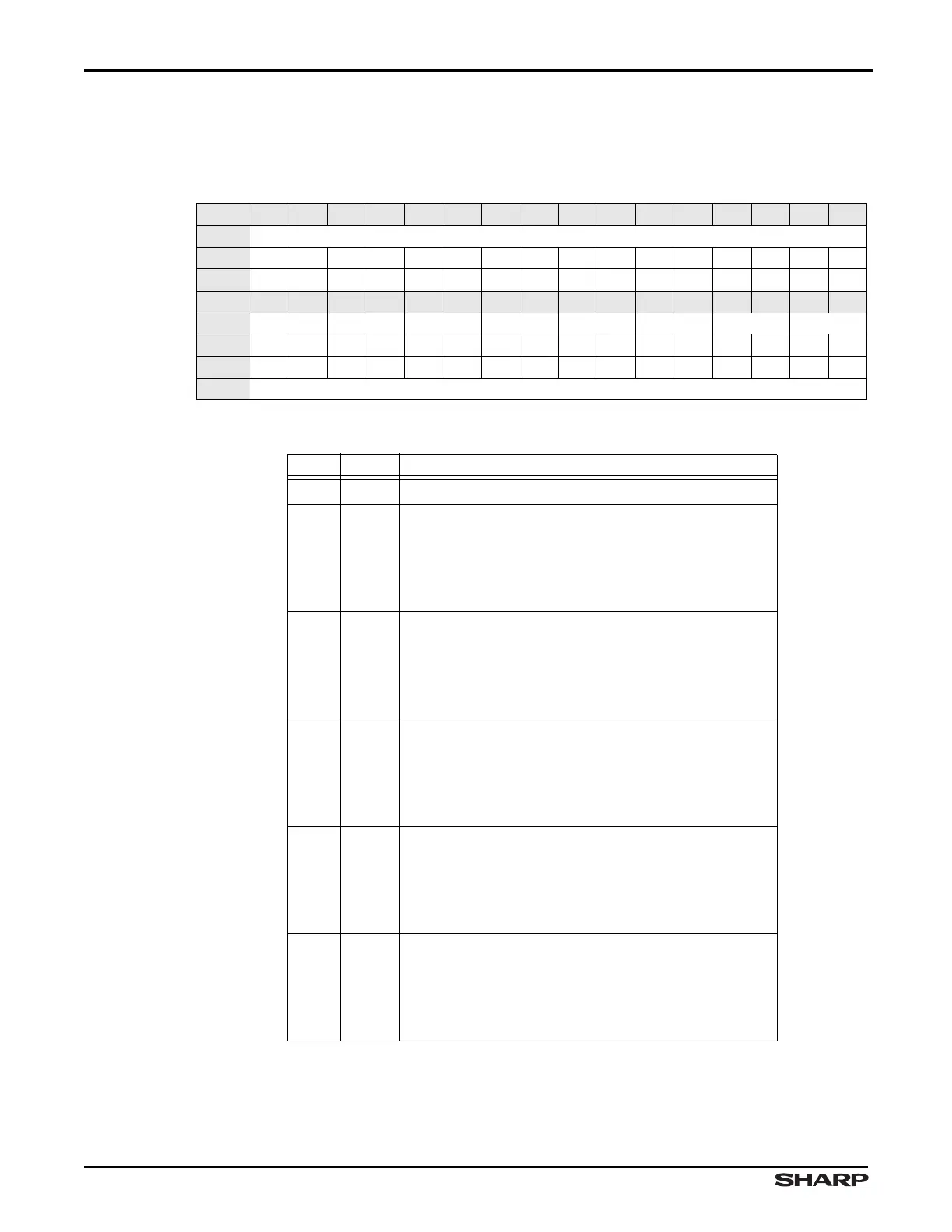

Table 11-61. MUXCTL22 Fields

BIT NAME DESCRIPTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:14 PF1

PF1/LCDVD7 Assignment

00 = PF1

01 = LCDVD7

10 = Reserved

11 = Reserved

13:12 PF0

PF0/LCDVD6 Assignment

00 = PF0

01 = LCDVD6

10 = Reserved

11 = Reserved

11:10 PG7

PG7/LCDVD5 Assignment

00 = PG7

01 = LCDVD5

10 = Reserved

11 = Reserved

9:8 PG6

PG6/LCDVD4 Assignment

00 = PG6

01 = LCDVD4

10 = Reserved

11 = Reserved

7:6 PG5

PG5/LCDVD3 Assignment

00 = PG5

01 = LCDVD3

10 = Reserved

11 = Reserved

Loading...

Loading...