Reset, Clock, and Power Controller LH79524/LH79525 User’s Guide

13-26 Version 1.0

13.2.2.16 SSP Clock Prescaler Register (SSPPRE)

The value in this register is used as a divisor for the Source Clock to derive the SSP clock

(SSPCLK) frequency. The SSP clock source (System Clock Oscillator, or HCLK) is

selected with the PCLKSEL1:SSP bit (see Section 13.2.2.13). Table 13-39 shows the

valid combinations for SSPDIV and the resulting SSP clock frequency. Following reset, the

prescaler is programmed to pass the clock through without division. All other SSPDIV val-

ues are invalid.

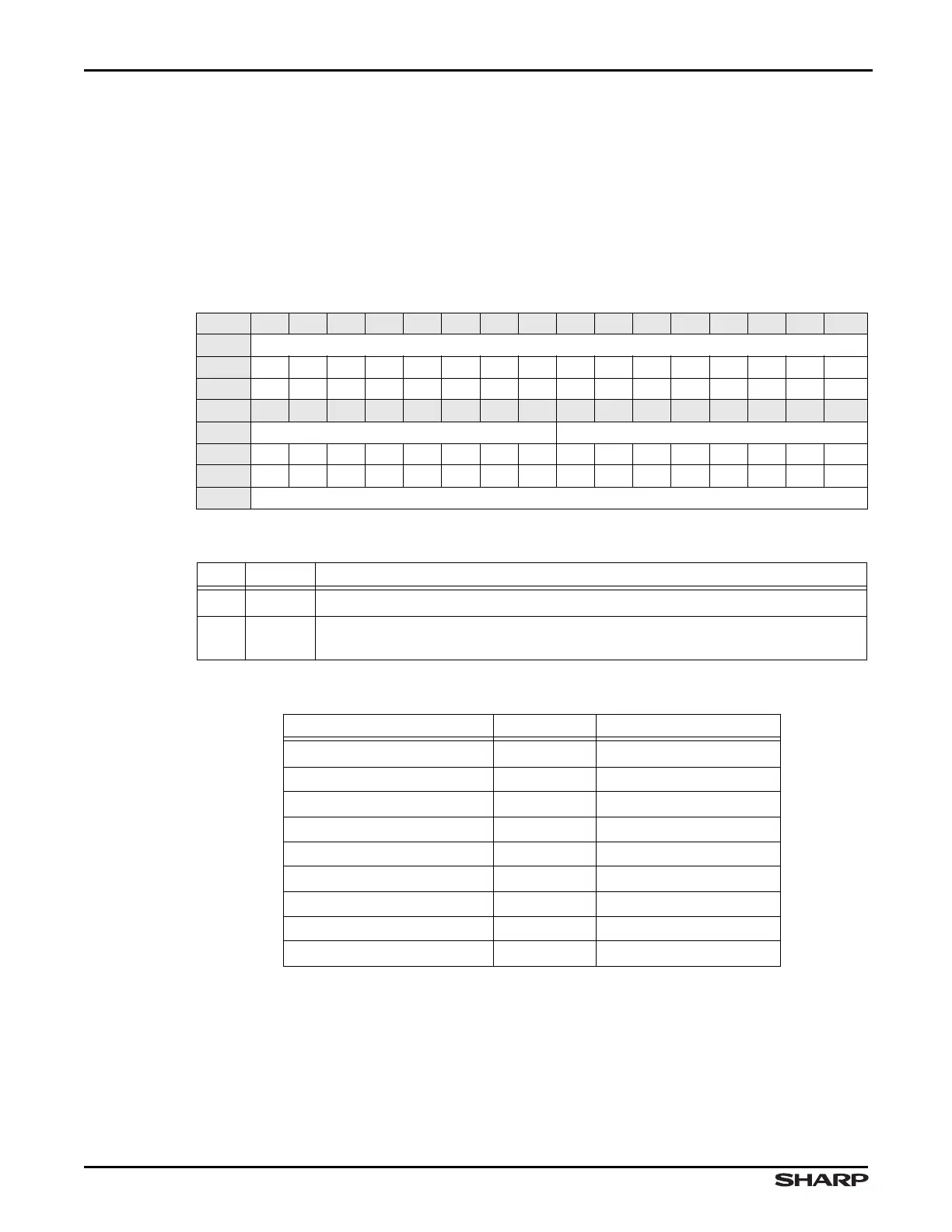

Table 13-37. SSPPRE Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 000000000000000 0

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// SSPDIV

RESET 000000000000000 0

RW RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFE2000 + 0x44

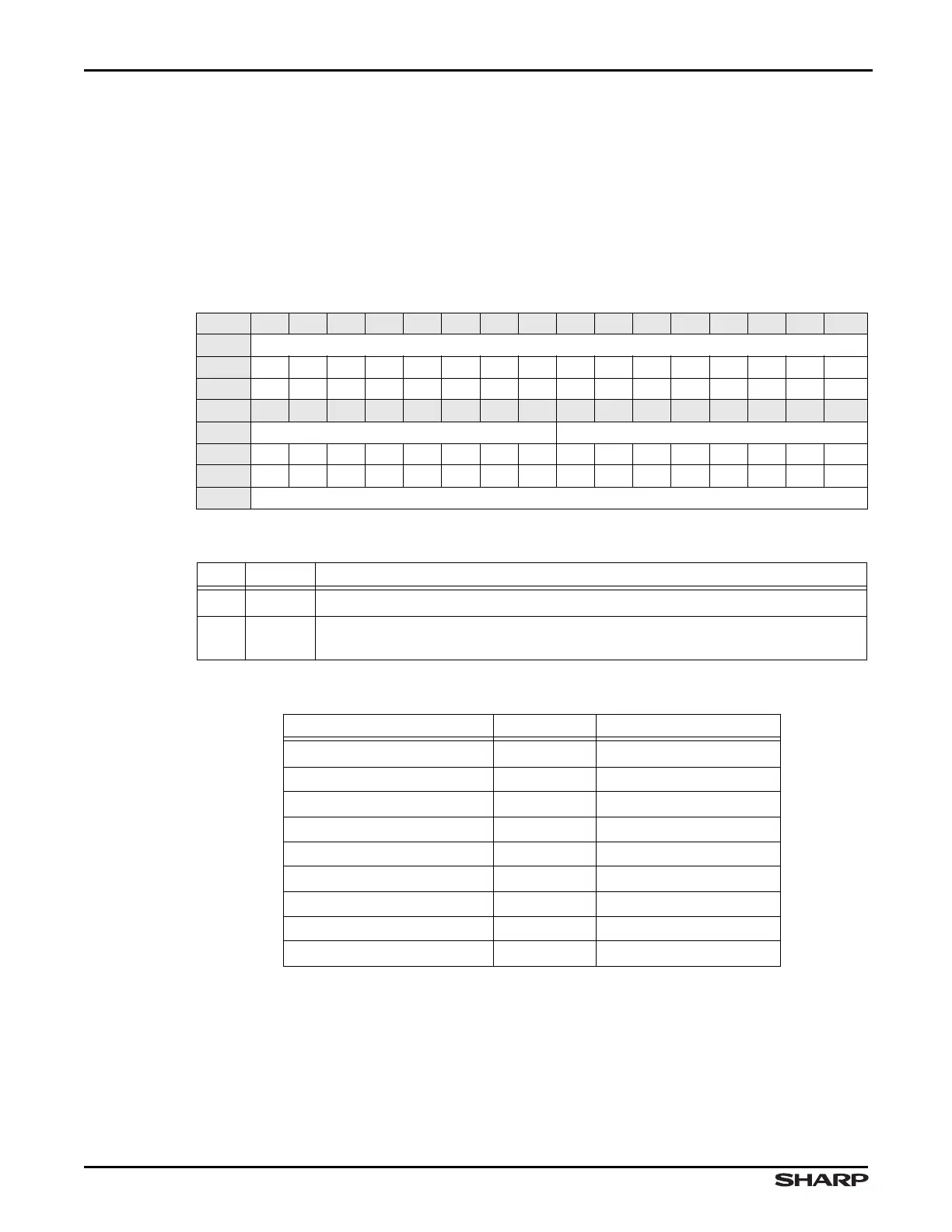

Table 13-38. SSPPRE Fields

BITS NAME DESCRIPTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7:0 SSPDIV

SSP Divisor Program with the clock source divisor for the SSP Clock

prescaler (see Table 13-39).

Table 13-39. SSPPRE Register Values

SSPDIV DIVISOR ƒ(SSP)

0b00000000 (default) 1 ƒ(clock source)

0b00000001 2 ƒ(clock source)/2

0b00000010 4 ƒ(clock source)/4

0b00000100 8 ƒ(clock source)/8

0b00001000 16 ƒ(clock source)/16

0b00010000 32 ƒ(clock source)/32

0b00100000 64 ƒ(clock source)/64

0b01000000 128 ƒ(clock source)/128

0b10000000 256 ƒ(clock source)/256

Loading...

Loading...