LH79524/LH79525 User’s Guide External Memory Controller

Version 1.0 7-47

7.5.2.18 Static Memory Extended Wait Register (WAIT)

The Static Memory Extended Wait Register is used to time long static memory read and

write transfers (longer than can be supported by the SWAITRD or SWAITWR registers)

when the EW bit of the SCONFIG register is enabled. There is only a single WAIT register.

These registers should only be modified during system initialization, or when there are

no current or outstanding transactions. Software can ensure that there are no current or

outstanding transactions by waiting until the memory controller is idle, then entering

Low-Power Mode (CONTROL:MODE = 1), or Disable Mode (CONTROL:ENABLE = 0).

When in these two modes, external memory access is not allowed, ensuring that

changing parameters will not corrupt external data. Low-Power Mode automatically

refreshes SDRAM; Disable Mode requires commanding the SDRAM to Self Refresh

(DYNMCTRL:SR = 1) prior to entering Disable.

However, if necessary, these control bits

can be altered during normal operation.

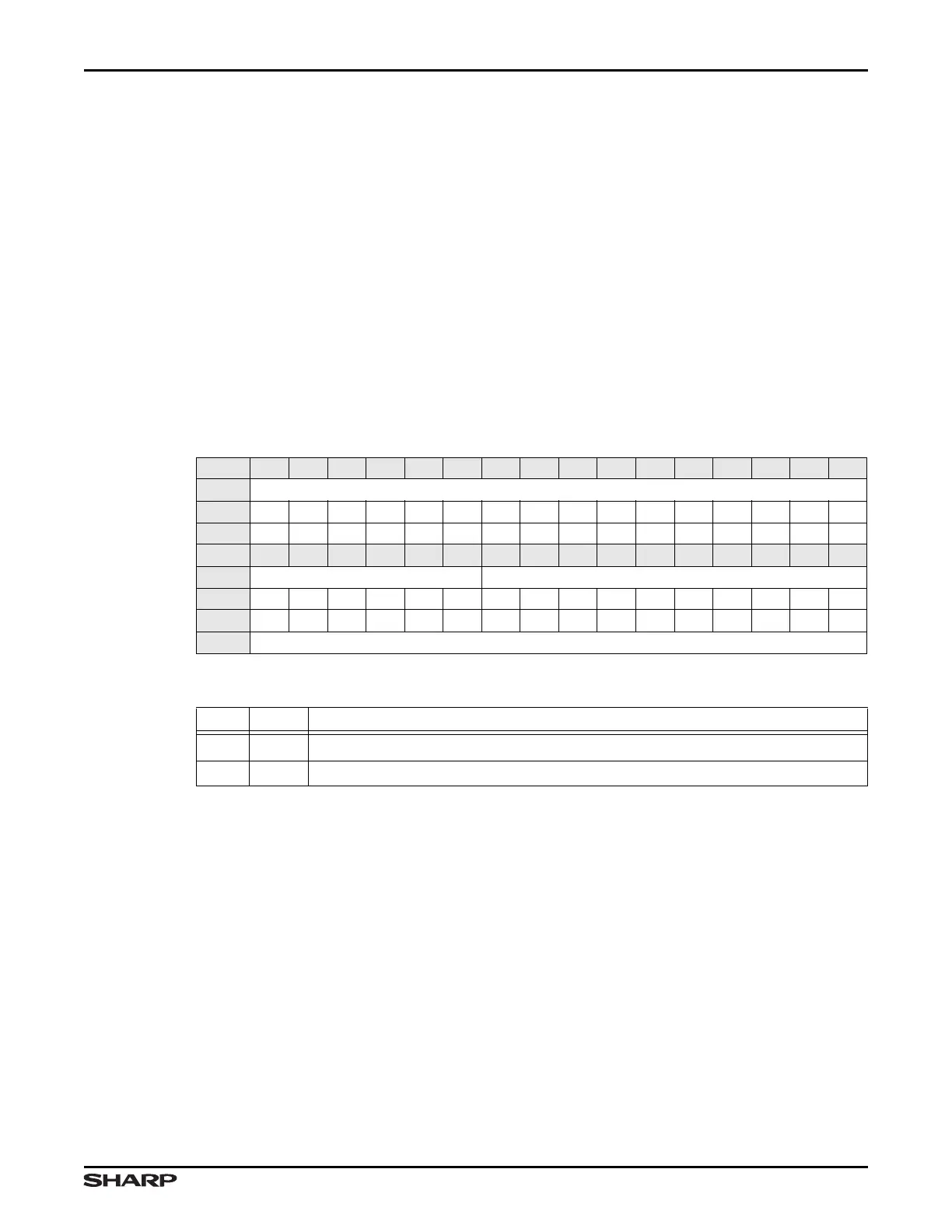

Table 7-45. WAIT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// WAIT

RESET 0000000000000000

TYPE RO RO RO RO RO RO RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFF1000 + 0x080

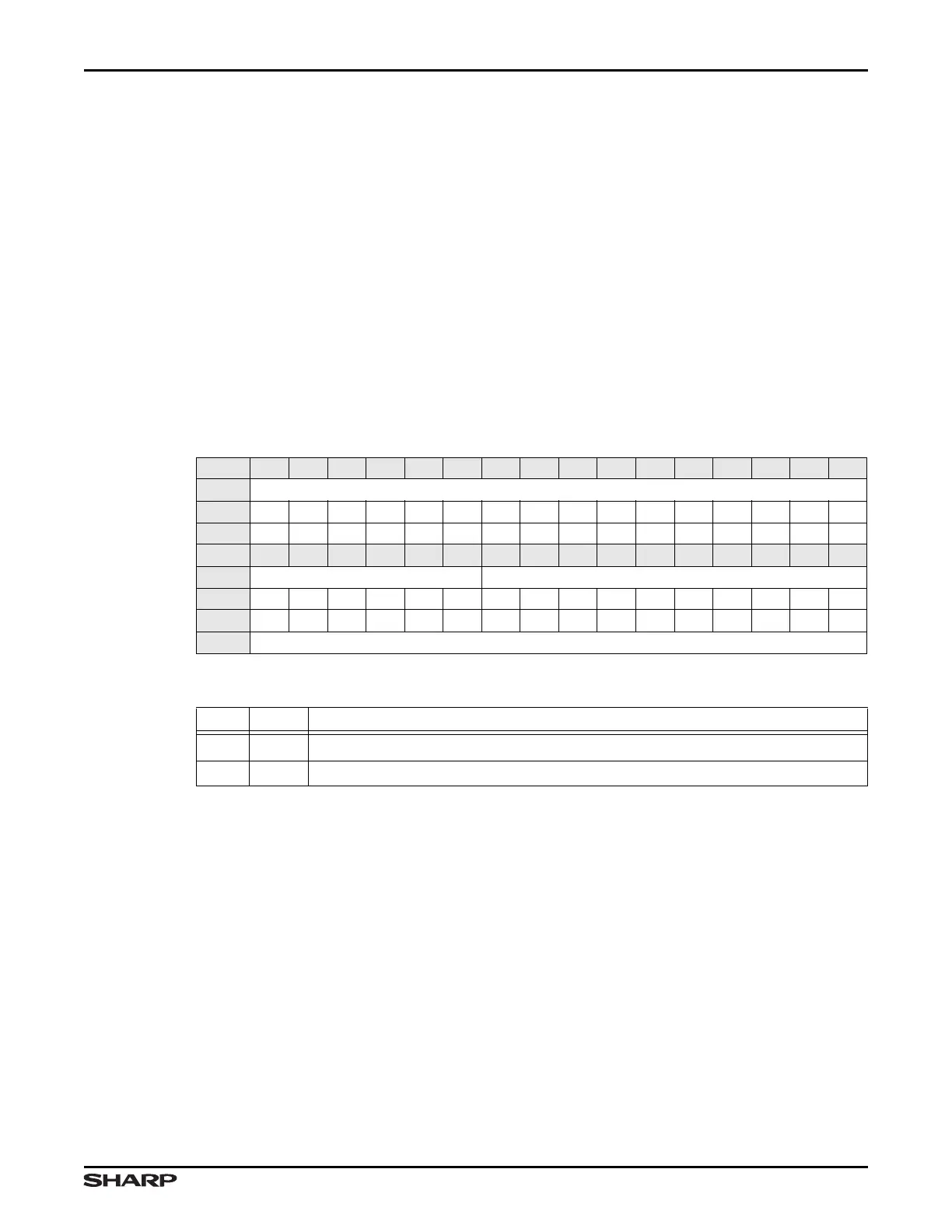

Table 7-46. WAIT Fields

BITS NAME FUNCTION

31:10 /// Reserved Reading returns 0. Write the reset value.

9:0 WAIT External Wait Time Out Wait Time Out = (WAIT+1) x 16 HCLK clock periods

Loading...

Loading...