Ethernet MAC Controller LH79524/LH79525 User’s Guide

6-18 Version 1.0

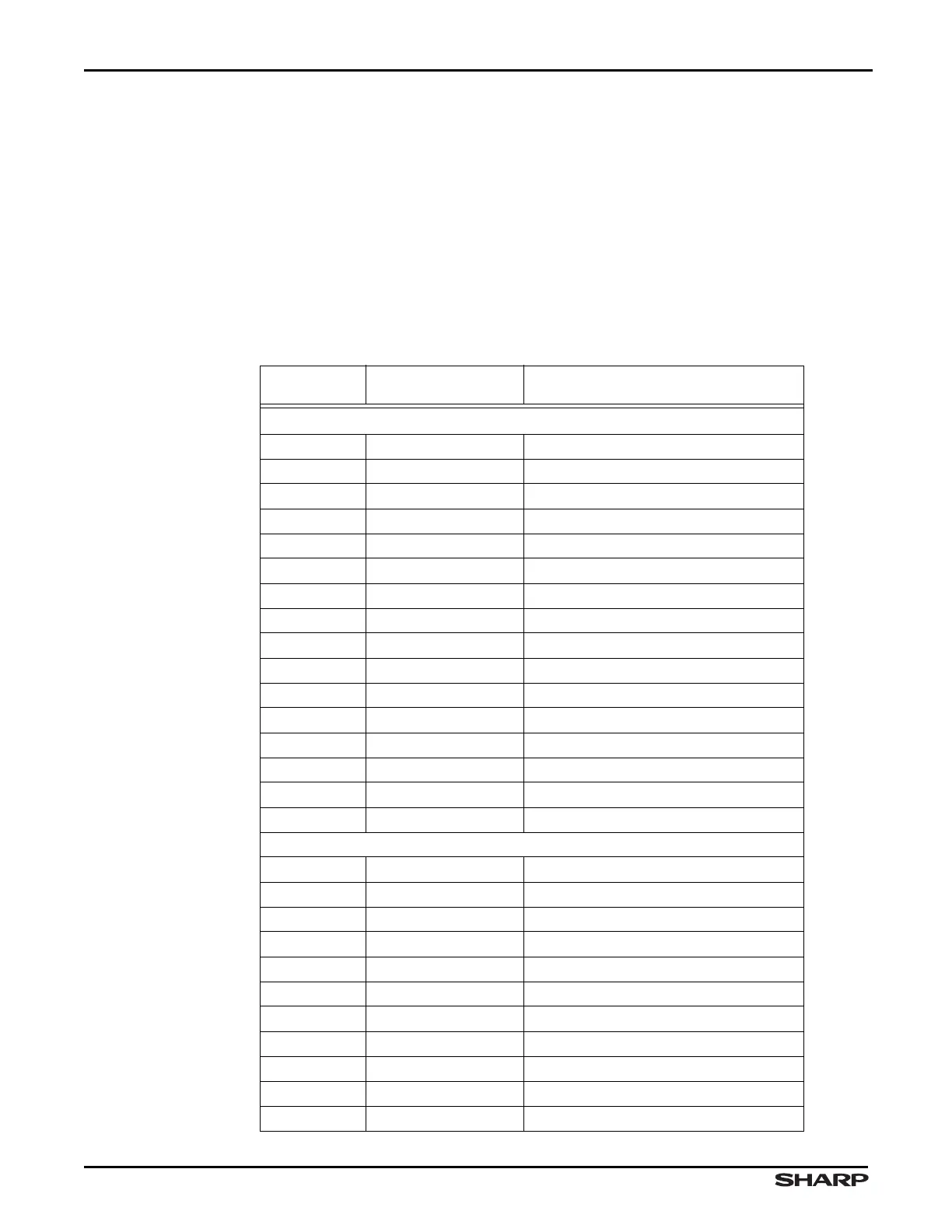

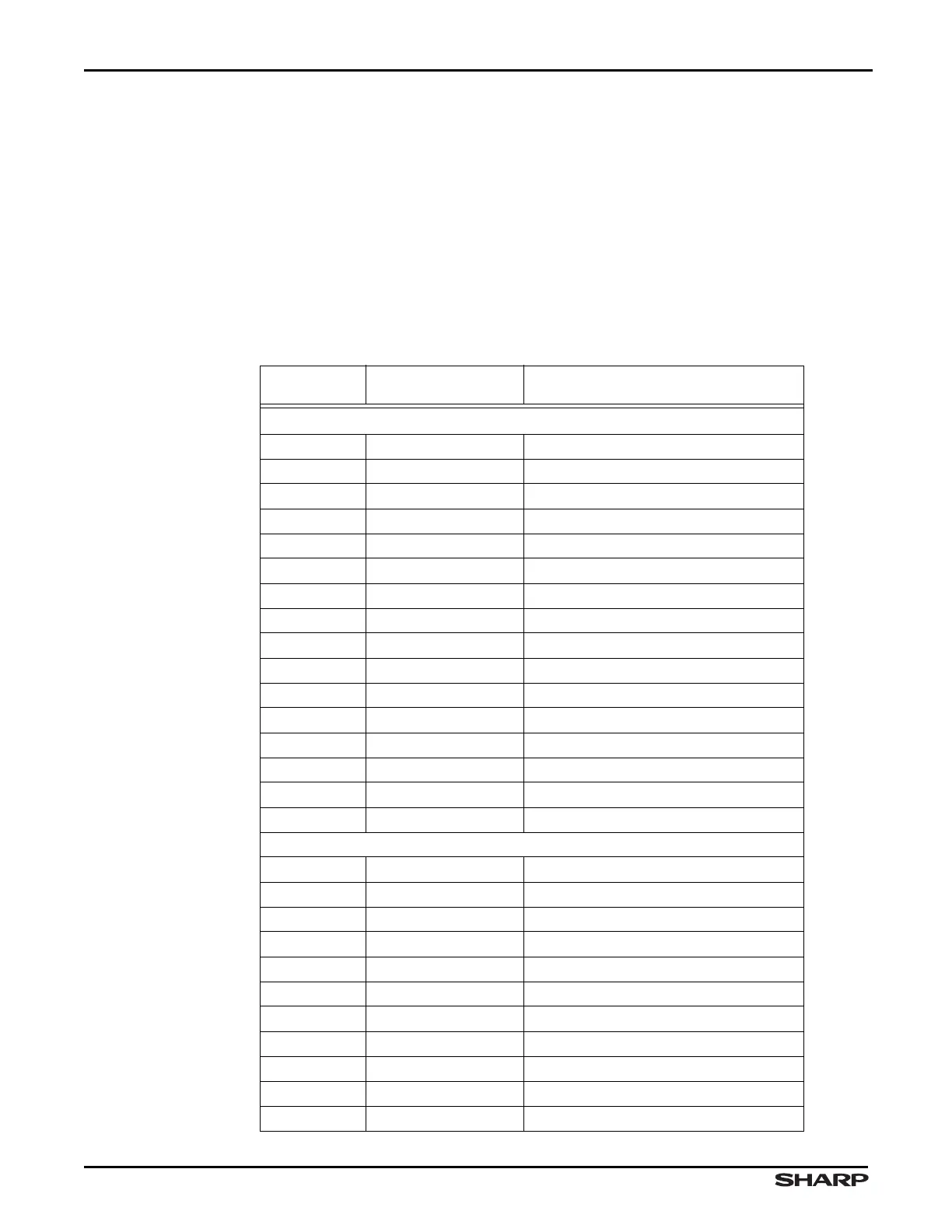

6.3 Register Reference

This section provides the EMAC register memory mapping and bit fields.

6.3.1 Memory Map

The base address for the EMAC is 0xFFFC7000.

Table 6-5 Summarizes the EMAC registers. There are three types of registers in the EMAC:

control, configuration, and status registers; statistics registers; and matching registers.

Address offsets in the table are from the base address. All registers are little endian format.

Table 6-5. EMAC Register Summary

ADDRESS

OFFSET

NAME DESCRIPTION

CONTROL, CONFIGURATION, AND STATUS REGISTERS

0x00 NETCTL Network Control Register

0x04 NETCONFIG Network Configuration Register

0x08 NETSTATUS Network Status Register

0x0C /// Reserved

0x10 /// Reserved

0x14 TXSTATUS Transmit Status Register

0x18 RXBQP Receive Buffer Queue Pointer

0x1C TXBQP Transmit Buffer Queue Pointer

0x20 RXSTATUS Receive Status Register

0x24 INSTATUS Interrupt Status Register

0x28 ENABLE Interrupt Enable Register

0x2C DISABLE Interrupt Disable Register

0x30 MASK Interrupt Mask Register

0x34 PHYMAINT PHY Maintenance Register

0x38 PAUSETIME Pause Time Register

0xBC TXPAUSEQUAN Transmit pause quantum

STATISTICS REGISTERS

0x3C PAUSEFRRX Pause Frames Received

0x40 FRMTXOK Frames Transmitted OK

0x44 SINGLECOL Single Collision Frames

0x48 MULTFRM Multiple Collision Frames

0x4C FRMRXOK Frames Received OK

0x50 FRCHK Frame Check Sequence Errors

0x54 ALIGNERR Alignment Errors

0x58 DEFTXFRM Deferred Transmission Frames

0x5C LATECOL Late collisions

0x60 EXCOL Excessive collisions

0x64 TXUNDER Transmit underrun errors

Loading...

Loading...