LH79524/LH79525 User’s Guide Direct Memory Access Controller

Version 1.0 5-9

5.2.2.4 Control Register (CTRL)

The Control Register contains the configuration of the DMA Controller. Constraints on the

field values based on the stream type are defined in Table 5-18. Where a value appears

in this table, that is the only valid value for that stream, and the field must be programmed

to this value.

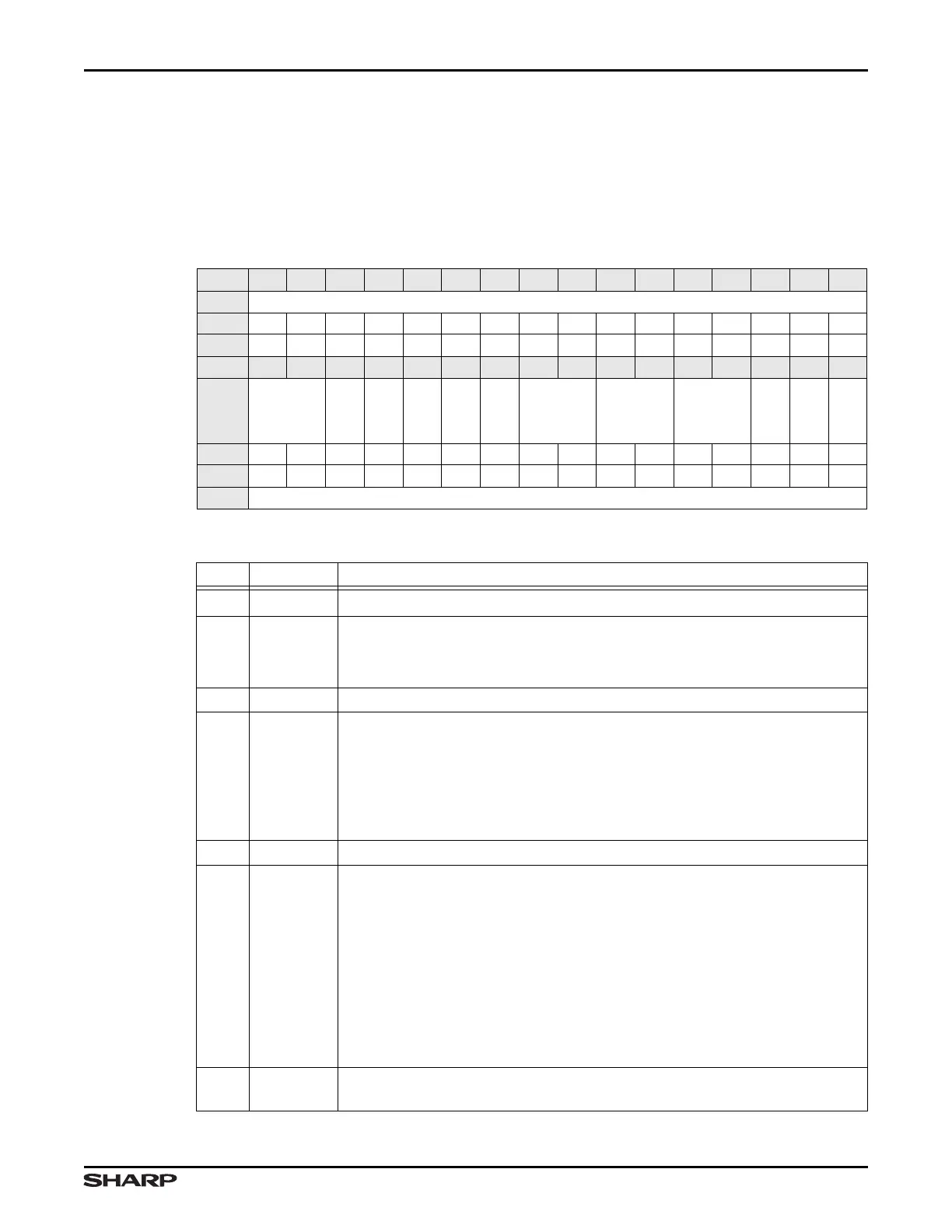

Table 5-14. CTRL Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// DIR /// M2M ///

ADMODE

DESIZE SOBURST SOSIZE

DEINC

SOINC

ENABLE

RESET 0000000000000000

RW RO RO RW RO RW RO RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFE1000 + 0x14

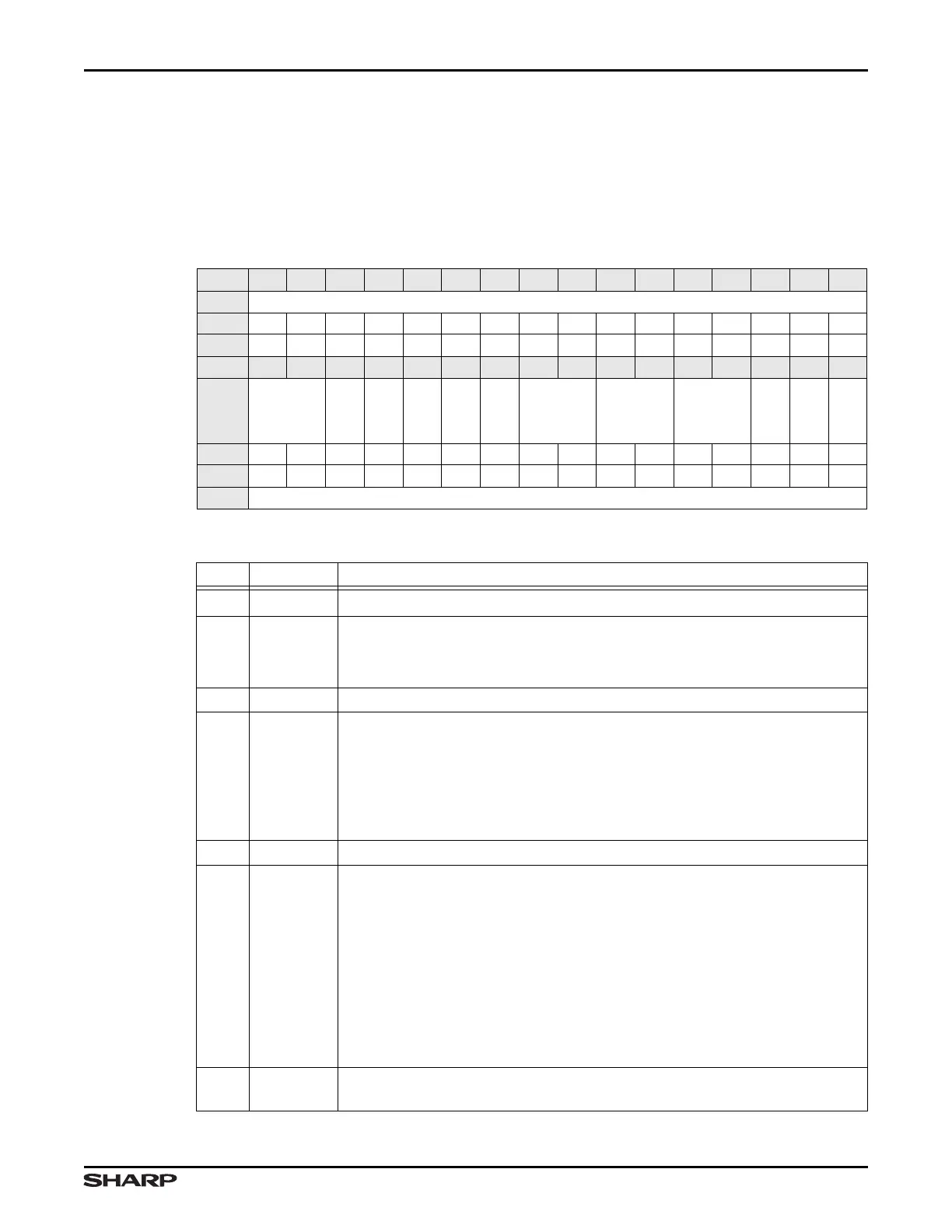

Table 5-15. CTRL Fields

BIT NAME DESCRIPTION

31:14 /// Reserved Reading returns 0. Write the reset value.

13 DIR

Peripheral is Source or Destination

1 = Peripheral is the destination

0 = Peripheral is the source

12 /// Reserved Reading returns 0. Write the reset value.

11 M2M

Stream 3 Memory Transfer Selects memory-to-memory transfer for

Stream 3. Ignored for data streams[2:0].

1 = Stream 3 is configured for memory-to-memory transfer. The DMA

Controller disregards any request from UART0TX and transfers data

from source to destination as fast as possible until MaxCnt expires

0 = Stream 3 is not configured for memory-to-memory transfer

10 /// Reserved Reading returns 0. Write the reset value.

9ADMODE

Current Source/Destination Loading Determines whether the Current

Source Address Register and the Current Destination Address Register load

from the Source Base Registers and the Destination Base Registers, re-

spectively, when the DMA Controller is enabled.

1 = Incremental Address Mode for source and destination. Registers are not

reloaded from their respective Base Address Registers when the DMA

Controller is enabled

0 = Wrapping Address Mode for source and destination. Registers load from

their respective Base Address Registers when the DMA Controller is

enabled. (default)

8:7 DESIZE

DMA-to-Destination Data Width Specifies the DMA-to-destination data

width. See Table 5-16.

Loading...

Loading...