LH79524/LH79525 User’s Guide Universal Serial Bus Device

Version 1.0 17-17

17.2.2.8 Interrupt Enable Register (UIE)

UIE provides interrupt enable bits for the interrupts in UIR. Following reset, only the USB

RESET and the RESUME interrupts are enabled.

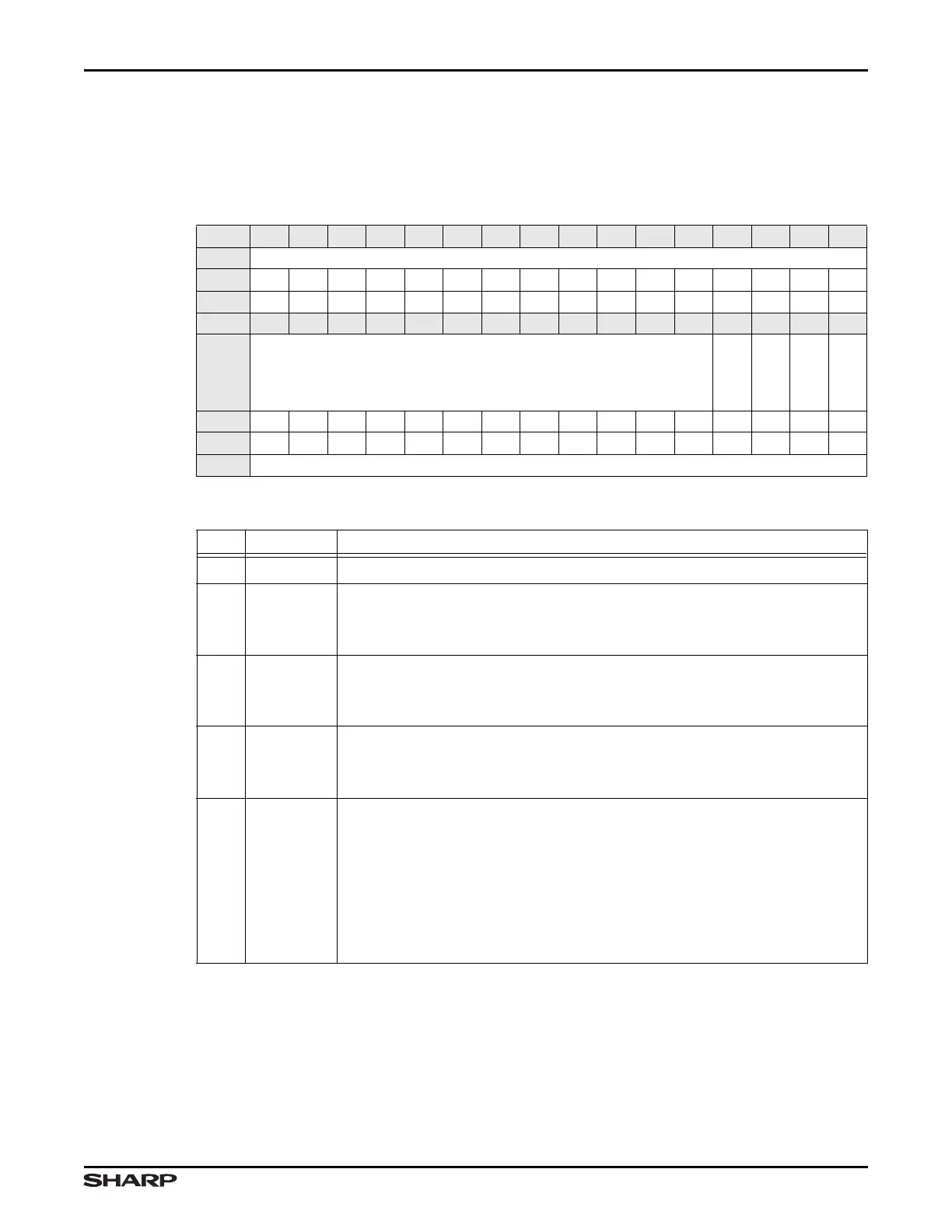

Table 17-18. UIE Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

SOFINTEN

URINTEN

RESINTEN

SUSINTEN

RESET 0000000000000110

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW

ADDR 0xFFFF5000 + 0x02C

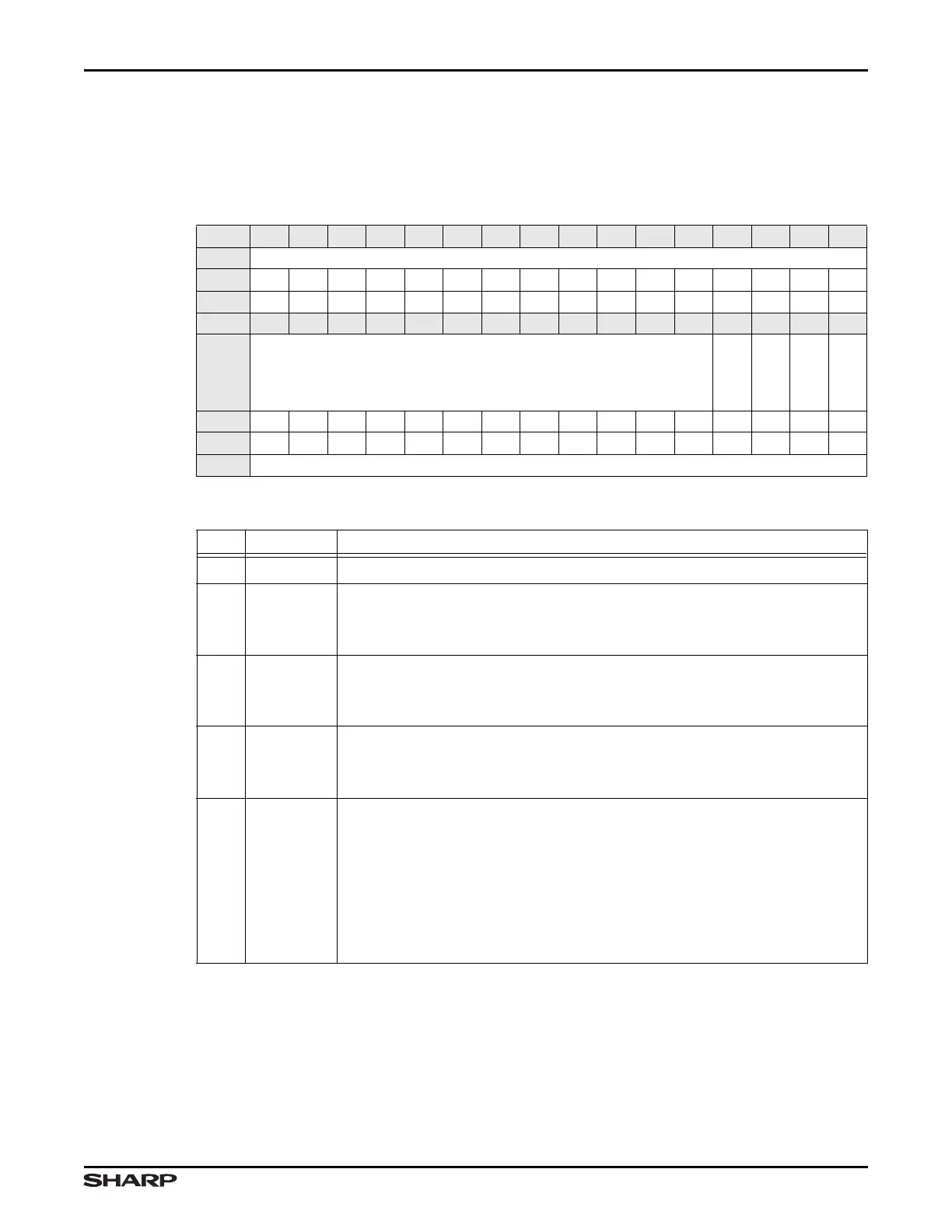

Table 17-19. UIE Fields

BITS NAME FUNCTION

31:3

/// Reserved Reading returns 0. Write the reset value.

3SOFINTEN

SOF Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

2 URINTEN

USB RESET Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

1 RESINTEN

RESUME Interrupt Enable

1 = Interrupt enabled

0 = Interrupt disabled

0SUSINTEN

SUSPEND Interrupt Enable Software programs this bit to 1 to enable an

Interrupt when it receives SUSPEND signalling. This bit is set whenever

there is no activity for 3 ms on the bus. Thus, if the CPU does not stop the

clock after the first SUSPEND interrupt, it will continue to be interrupted ev-

ery 3 ms as long as there is no activity on the USB bus. Following reset, this

interrupt is disabled.

1 = Interrupt enabled

0 = Interrupt disabled

Loading...

Loading...