Ethernet MAC Controller LH79524/LH79525 User’s Guide

6-44 Version 1.0

6.3.3.13 Receive Resource Errors (RXRERR)

This register counting the number of frames that were address matched but could not be copied to

memory because no receive buffer was available.

6.3.3.14 Receive Overrun Errors (RXOVERR)

Recieve overrun errors are tabulated in this register.

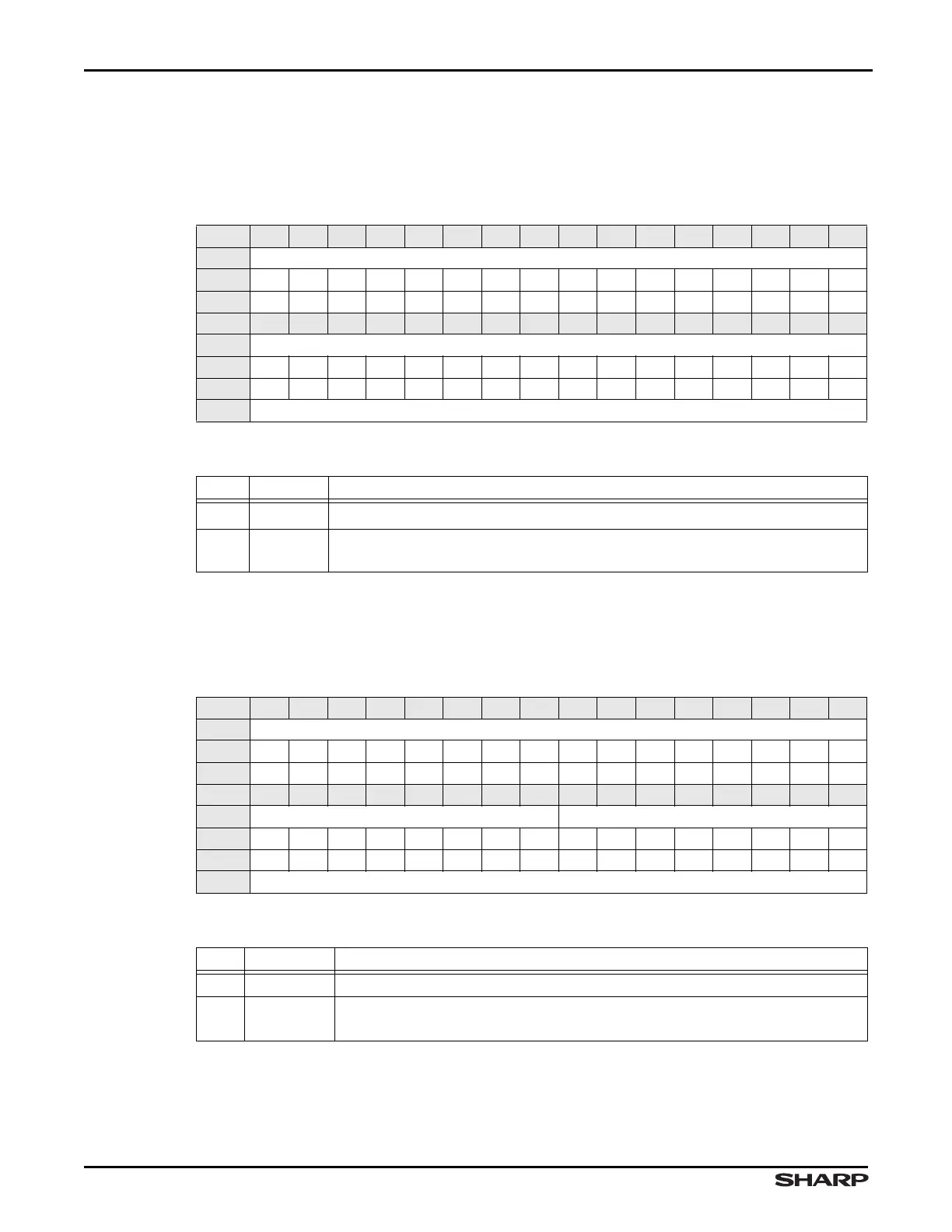

Table 6-58. RXRERR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD RXRERR

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x6C

Table 6-59. RXRERR Fields

BITS NAME FUNCTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:0 RXRERR

Receive Resource Errors The number of frames that were address matched

but could not be copied to memory because no receive buffer was available.

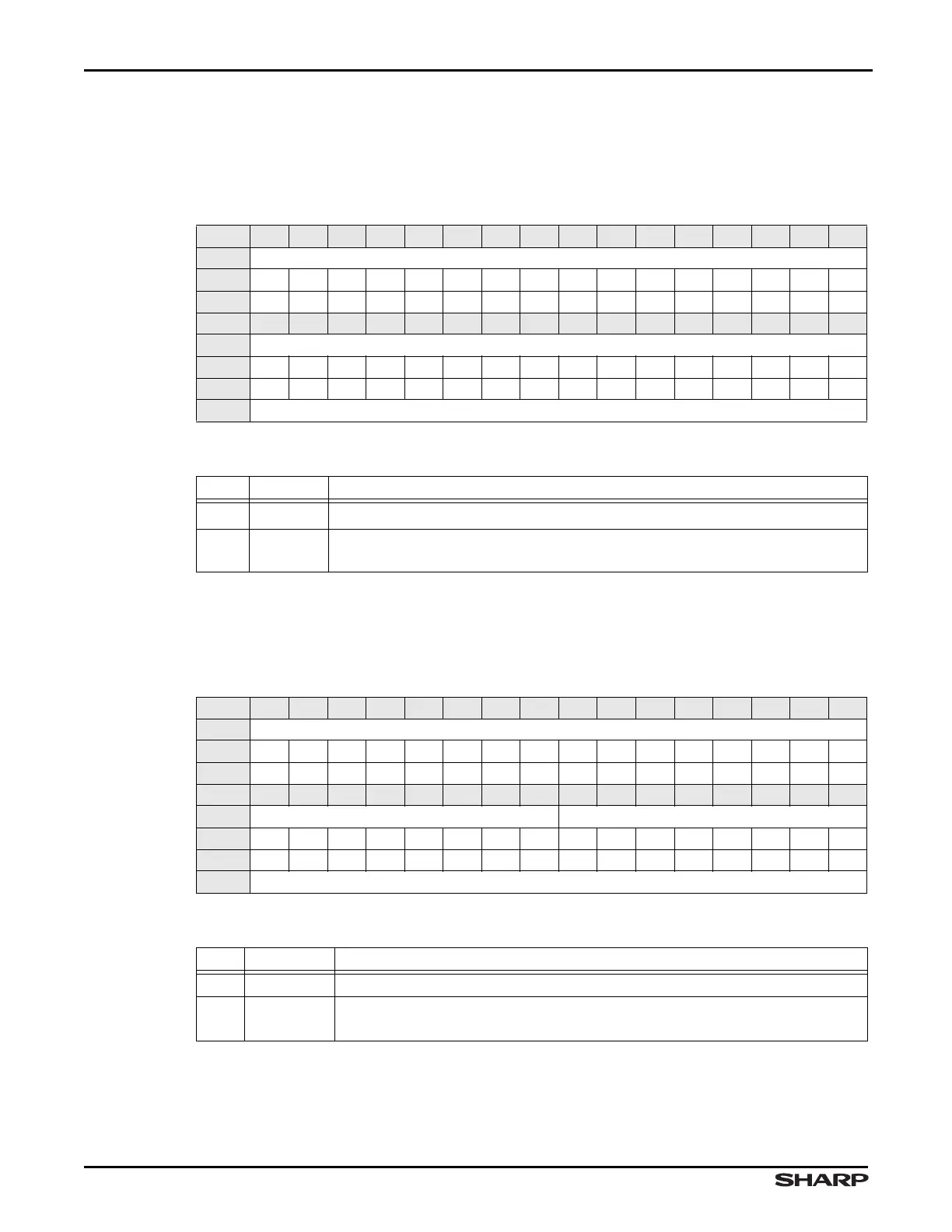

Table 6-60. RXOVERR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0 000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// RXOVERR

RESET 0 000000000000000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x70

Table 6-61. RXOVERR Fields

BITS NAME FUNCTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7:0 RXOVERR

Receive Overruns Number of frames that are address recognized but

were not copied to memory due to a receive DMA overrun.

Loading...

Loading...