Reset, Clock, and Power Controller LH79524/LH79525 User’s Guide

13-18 Version 1.0

13.2.2.8 CPU Clock Prescaler Register (CPUCLKPRE)

FCLK is the CPU Clock. This register allows a divisor to be programmed that is used to

divide the system PLL frequency to derive FCLK. The prescaled FCLK frequency is

defined by:

Following reset, the prescaler is programmed to divide by 30. Table 13-21 shows example

values for FDIV. The CPU clock must always be greater than or equal to the system bus

clock. Thus when changing clock dividers, the CPU frequency should be increased

BEFORE, decreased AFTER, and always kept at least equal to the system bus frequency.

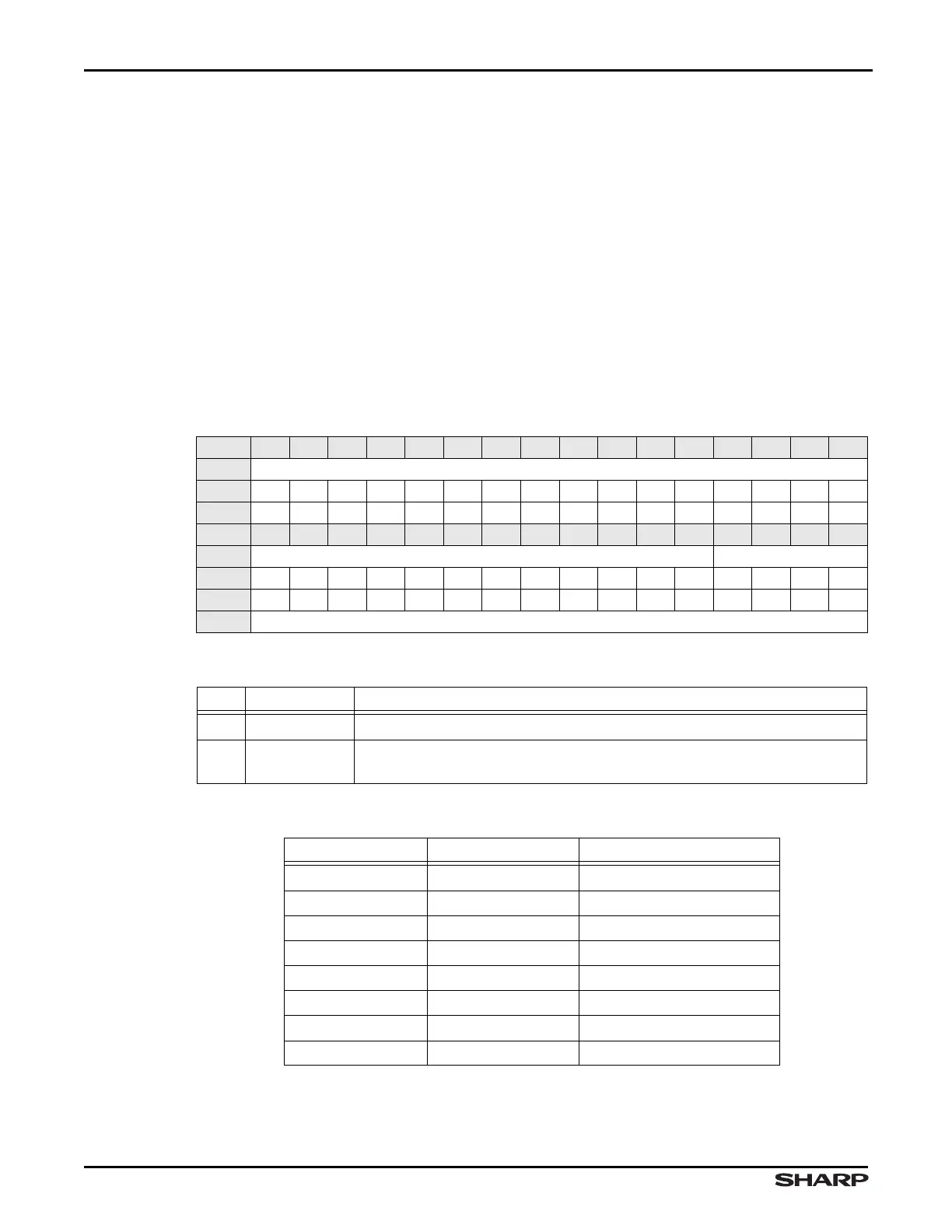

Table 13-19. CPUCLKPRE Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// FDIV

RESET 0000000000001111

RW RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW

ADDR 0xFFFE2000 + 0x1C

Table 13-20. CPUCLKPRE Fields

BITS NAME DESCRIPTION

31:4 /// Reserved Reading returns 0. Write the reset value.

3:0 FDIV

FCLK Divisor Program with the divisor for the HCLK prescaler. All FDIV

combinations are valid except 0b0000.

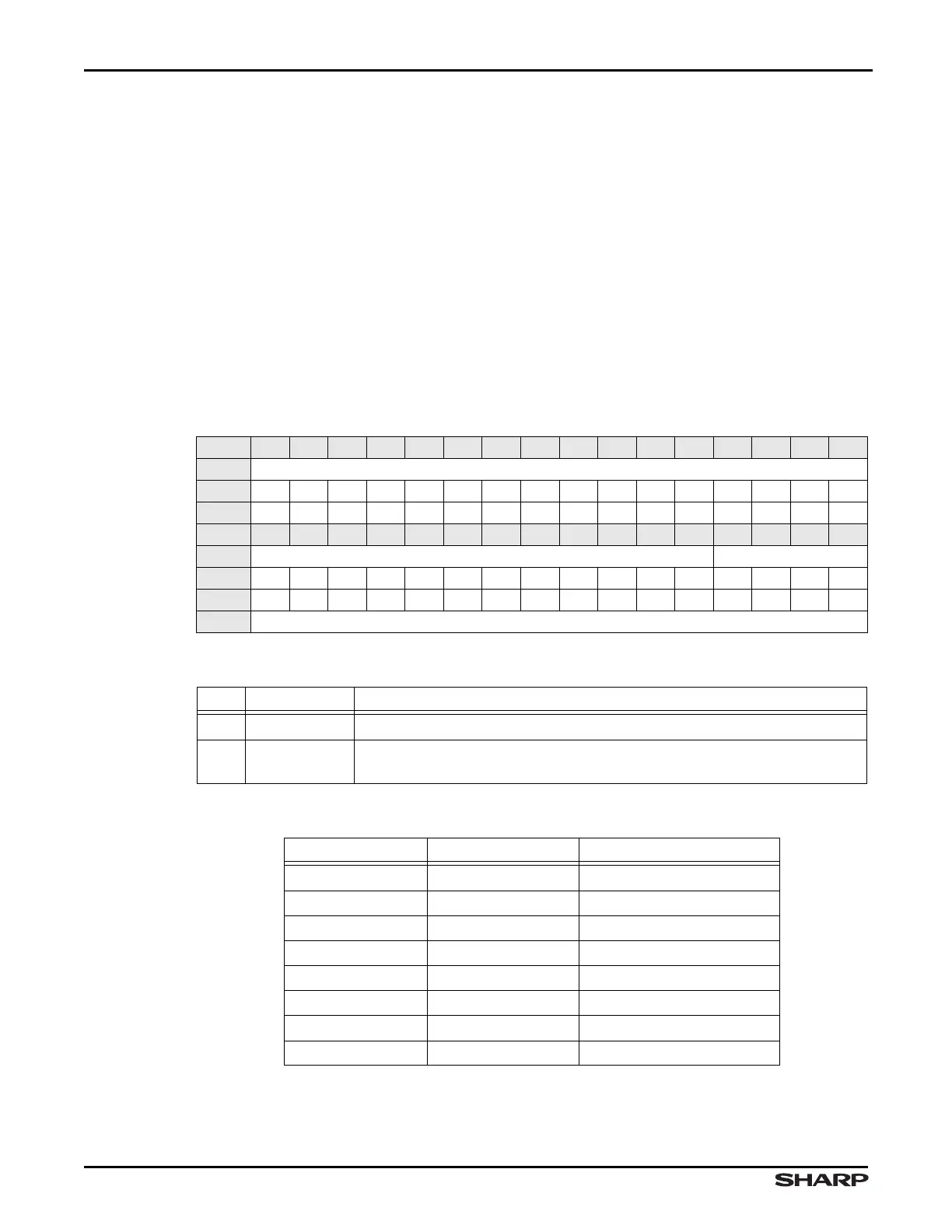

Table 13-21. CPUCLKPRE Register Values

FDIV DIVISOR VALUE ƒ(FCLK)

0b0000 — Invalid

0b0001 2 ƒ(System PLL)/2

0b0010 4 ƒ(System PLL)/4

0b0011 6 ƒ(System PLL)/6

0b0100 8 ƒ(System PLL)/8

0b0101 10 ƒ(System PLL)/10

:: :

0b1111 (default) 30 ƒ(System PLL)/30

ƒ(FCLK) ƒ

ƒ(SystemPLL)

2 FDIV×

--------------------------------------

⎝⎠

⎛⎞

=

Loading...

Loading...