LH79524/LH79525 User’s Guide External Memory Controller

Version 1.0 7-31

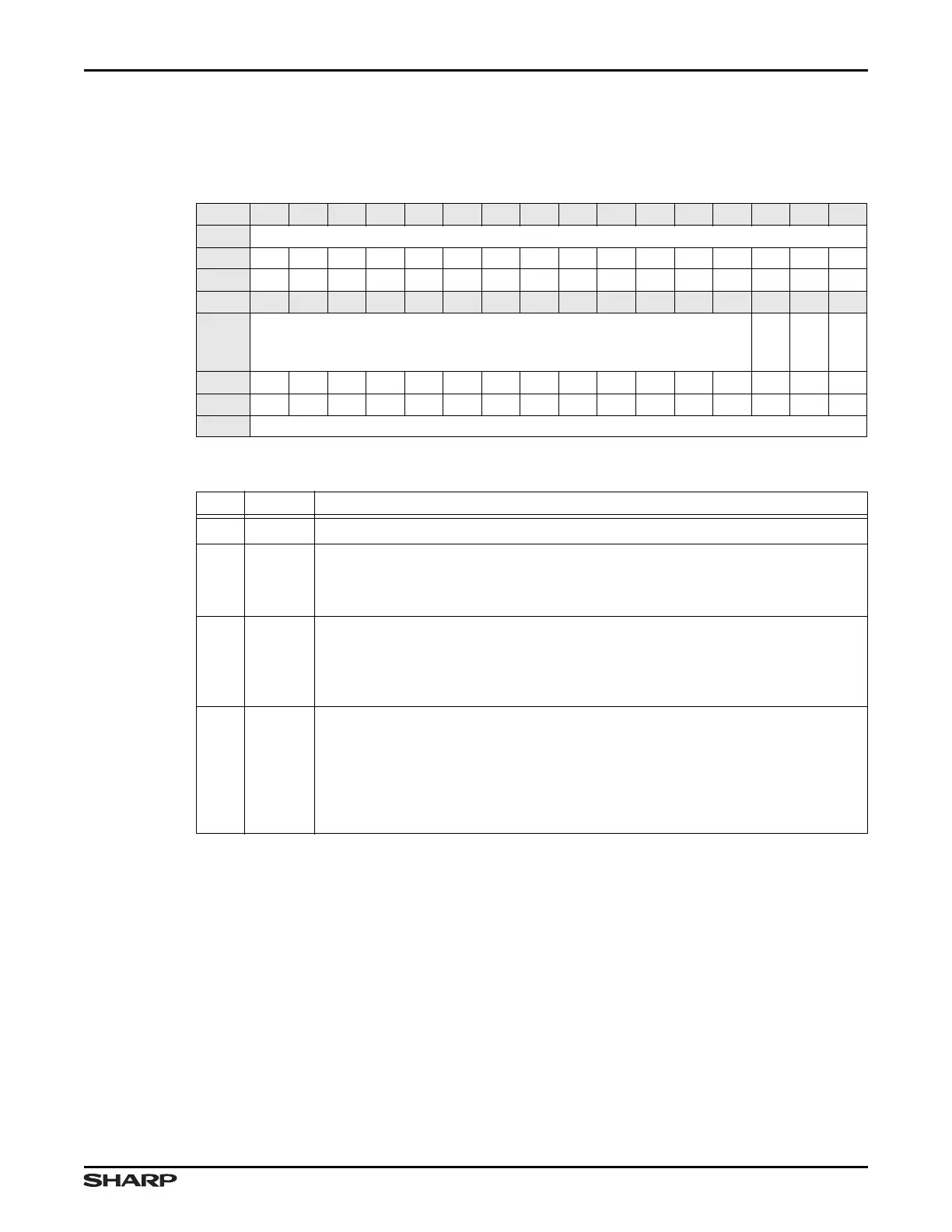

7.5.2.2 Status Register (STATUS)

The STATUS Register provides memory controller status information.

Table 7-13. STATUS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// SA

WRBUF

BUSY

RESET 0000000000000101

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR 0xFFFF1000 + 0x004

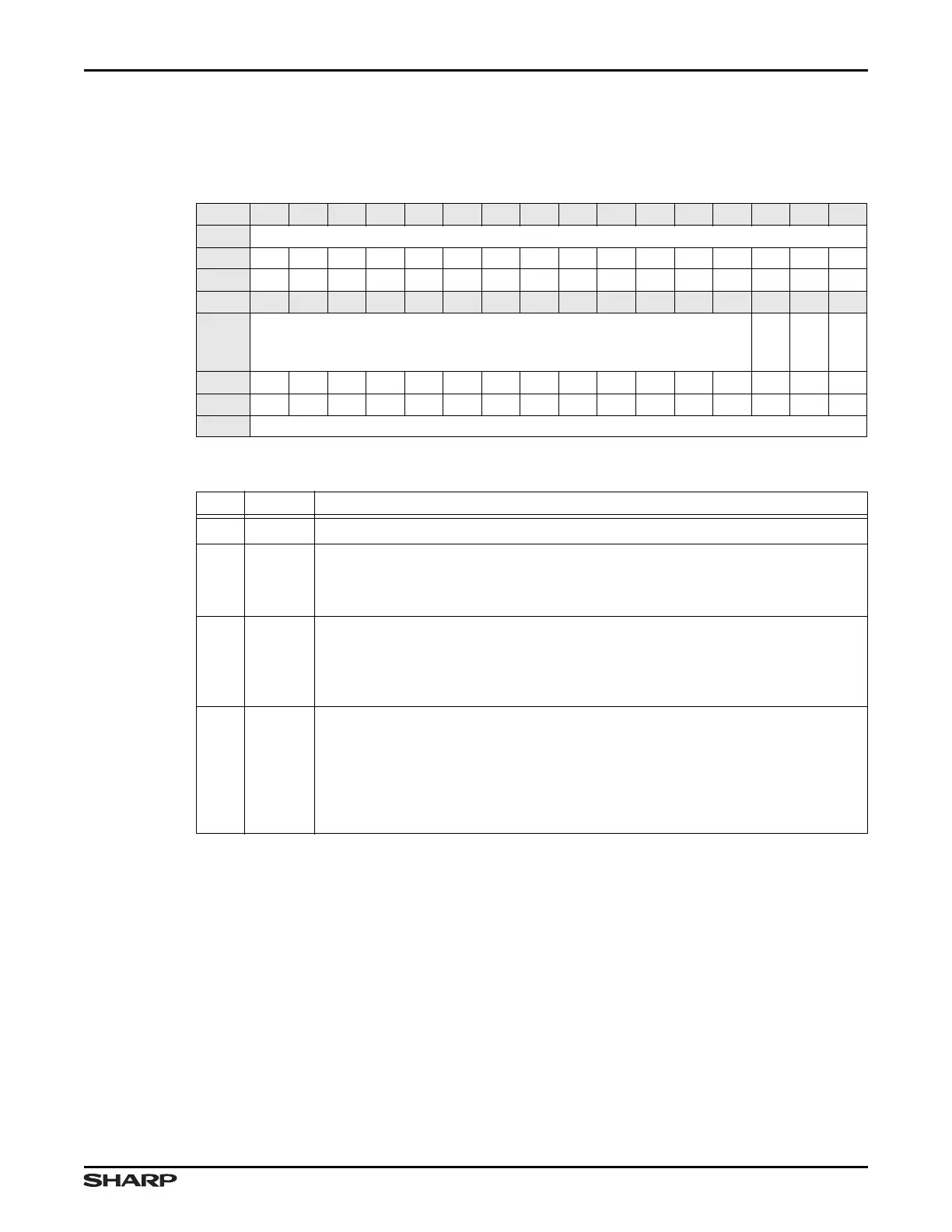

Table 7-14. STATUS Fields

BITS NAME FUNCTION

31:3 /// Reserved Reading returns 0. Write the reset value.

2SA

Self-refresh Acknowledge This bit indicates the operating mode of the EMC.

1 = Self-refresh Mode

0 = Normal Mode

1 WRBUF

Write Buffer Status This enables the EMC to enter low-power mode or dis-

abled mode cleanly by determining if the write buffers contain data or not.

1 = Write Buffers contain data

0 = Write Buffers empty

0BUSY

Busy This read-only bit is used to ensure that they memory controller enters

the low-power or disabled mode cleanly by determining if the memory controller

is busy or not.

1 = EMC is busy performing memory transactions, commands, auto-refresh

cycles, or is in self-refresh mode.

0 = EMC is idle

Loading...

Loading...