Ethernet MAC Controller LH79524/LH79525 User’s Guide

6-30 Version 1.0

6.3.2.8 Interrupt Status Register (INSTATUS)

The EMAC generates a single interrupt. This register indicates the source of this interrupt.

For test purposes each bit can be set or reset by directly writing to the interrupt status reg-

ister regardless of the state of the mask register. Otherwise the corresponding bit in the

MASK register must be cleared for a bit to be set. All bits are reset to zero on read. If any

bit is set in this register, the Ethernet Interrupt signal will be asserted

.

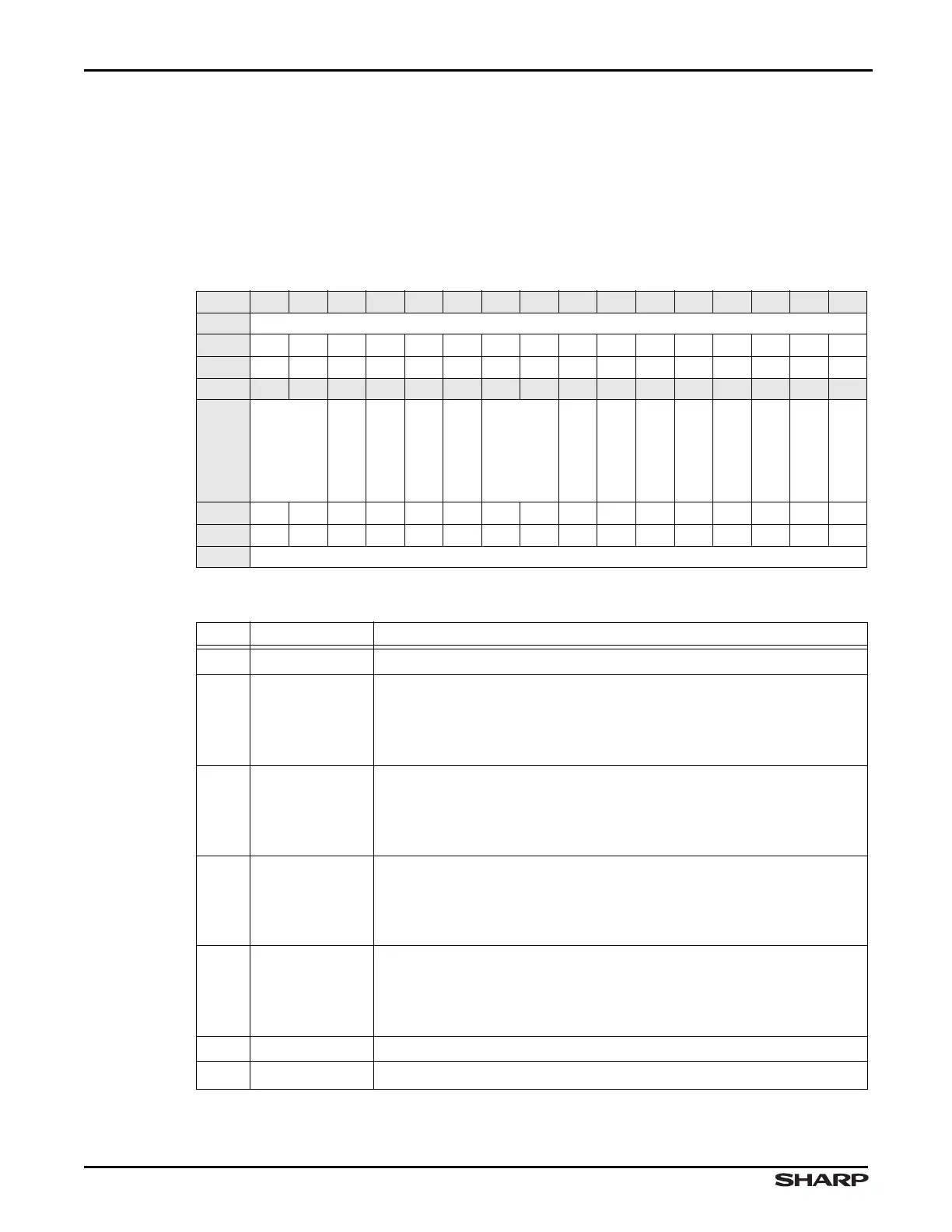

Table 6-20. INSTATUS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0

TYPE RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

PAUSEZERO

PAUSEFRRX

NOTOK

RECOVERRUN

///

TXCOMPLETE

TXBUFEXH

RETRYLIM

ETHTXBUFUR

TXUSDBITRD

RXUSDBITRD

RXCOMP

MNGFRMSENT

RESET 0 00000000000000

TYPE RO RW RW RW RW RW RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x24

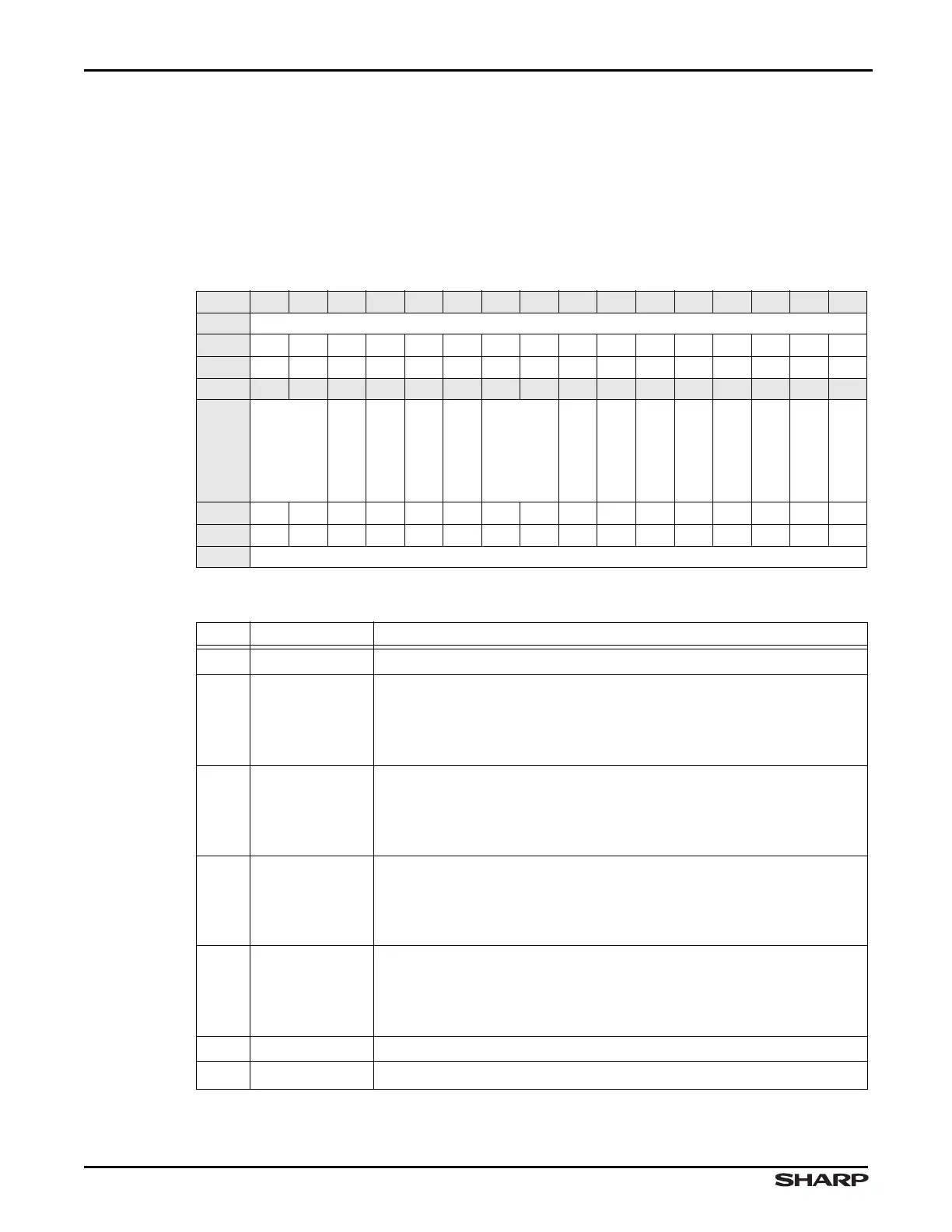

Table 6-21. INSTATUS Fields

BITS NAME FUNCTION

31:14 /// Reserved Reading returns 0. Write the reset value.

13 PAUSEZERO

Pause Time Zero Indicates the PAUSETIME register has decre-

mented to zero. This bit is reset to 0 when read.

1 = PAUSETIME decremented to zero

0 = PAUSETIME not decremented to zero

12 PAUSEFRRX

Pause Frame Received Indicates a valid Pause Frame has been

received. This bit is reset to 0 when read.

1 = Valid pause frame received

0 = No valid pause frame received

11 NOTOK

Response Not OK Indicates that the DMA Block receives response

‘Not OK’. This bit is reset to 0 when read.

1 = Response ‘Not OK’

0 = Normal operation

10 RECOVERRUN

Receive Overrun The DMA Block was unable to store the receive

frame to memory.

1 = Receive overrun

0 = No overrun

9

///

Reserved Reading returns 0. Write the reset value.

8 /// Reserved Reading returns 0. Write the reset value.

Loading...

Loading...