Vectored Interrupt Controller LH79524/LH79525 User’s Guide

18-12 Version 1.0

18.2.2.9 Vector Address Register (VECTADDR)

The Vector Address Register contains the ISR address of the currently active interrupt.

Reading this register provides the address of the ISR, and indicates to the priority hard-

ware that the interrupt is being serviced. Writing to this register indicates to the priority

hardware that the interrupt has been serviced.

The ISR can read the VECTADDR Register:

• When an IRQ interrupt is generated at the end of the ISR.

• When the VECTADDR Register is written to.

• To update the priority hardware.

Reading or writing to the register at other times can cause incorrect operation.

18.2.2.10 Default Vector Address Register (DEFVECTADDR)

This register contains the default ISR address. This address is used for non-vectored IRQs.

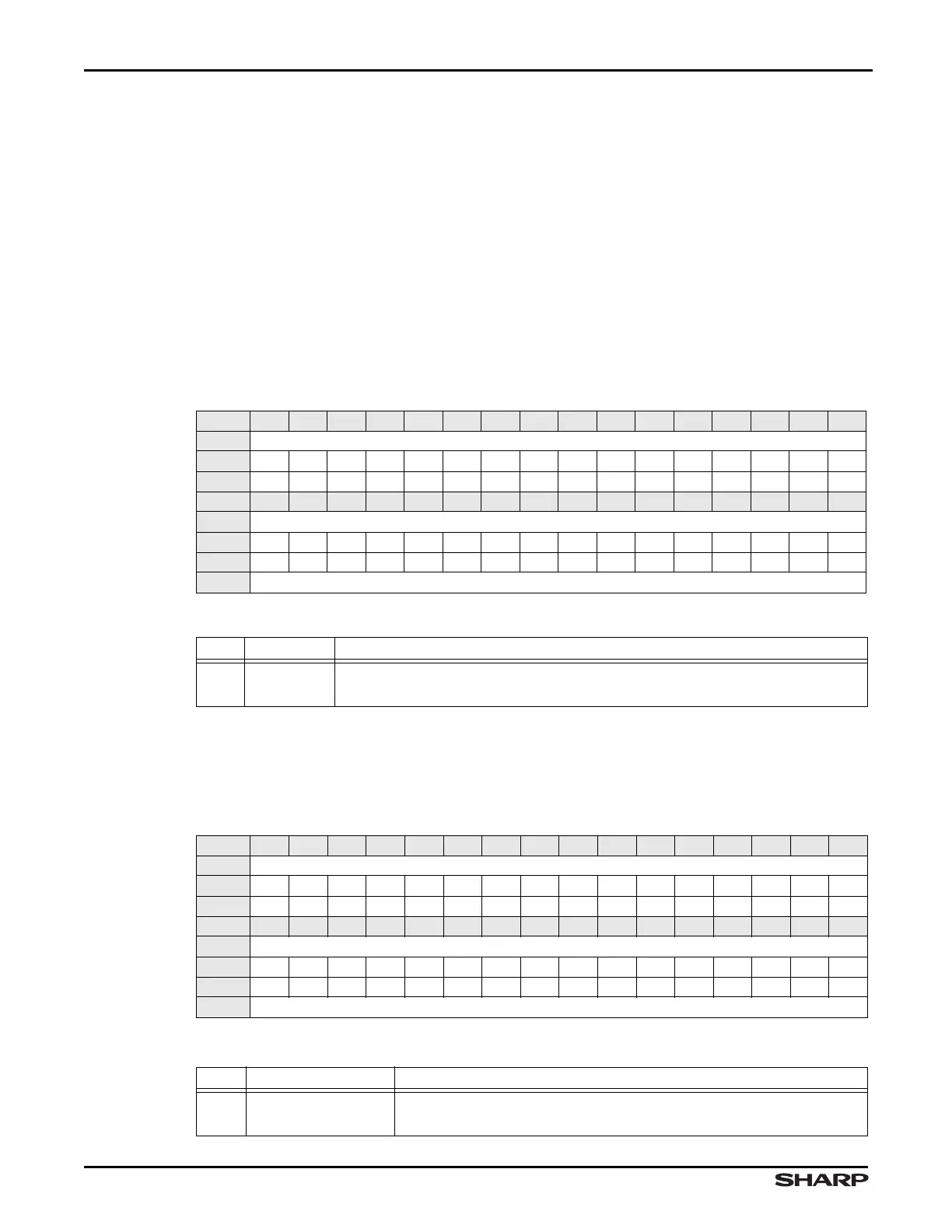

Table 18-19. VECTADDR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD VectorAddr

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD VectorAddr

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFFF000 + 0x030

Table 18-20. VECTADDR Fields

BITS NAME DESCRIPTION

31:0 VectorAddr

ISR Address Reading returns the address of the currently active ISR.

Writing clears the interrupt.

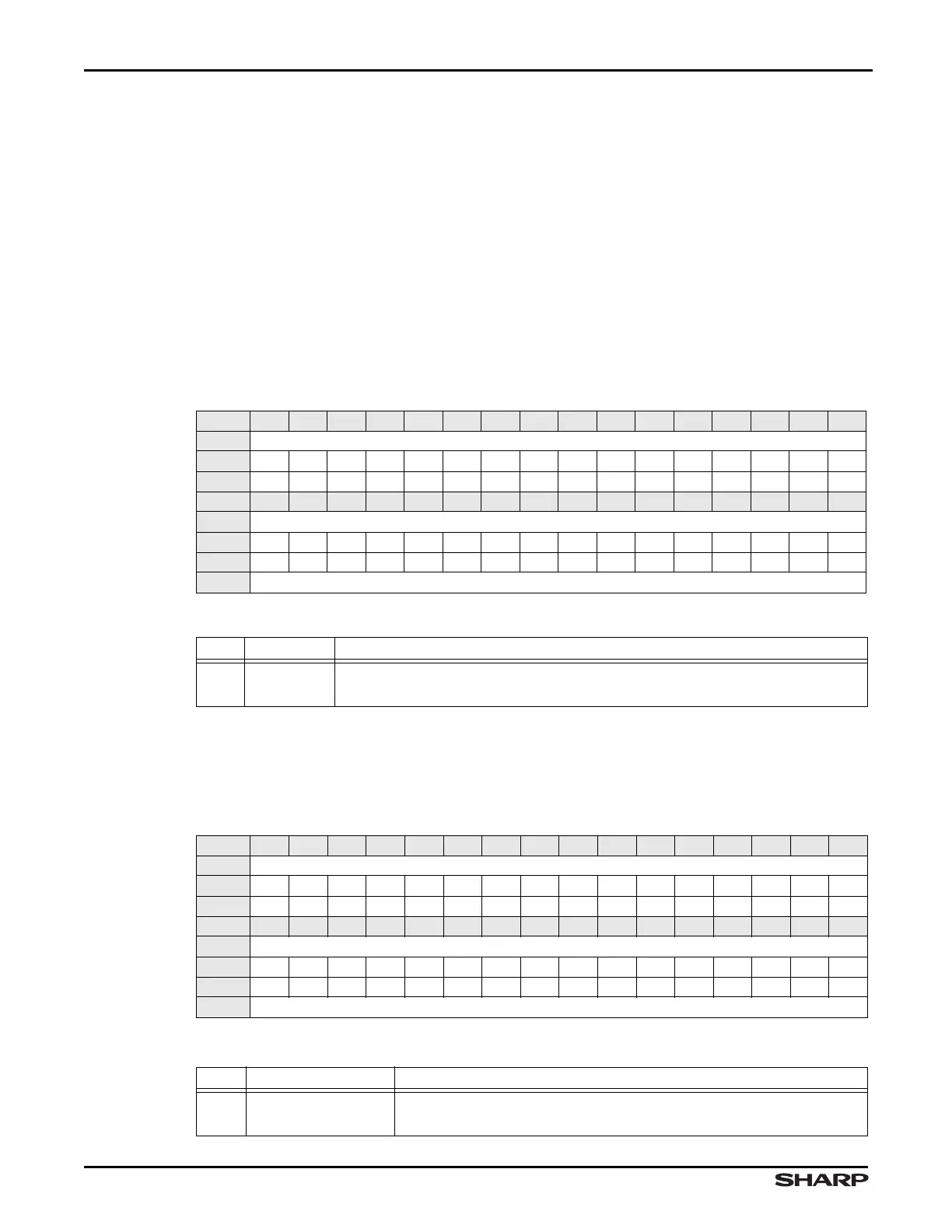

Table 18-21. DEFVECTADDR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD Default VectorAddr

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD Default VectorAddr

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFFF000 + 0x034

Table 18-22. DEFVECTADDR Fields

BITS NAME DESCRIPTION

31:0 Default VectorAddr

Default ISR Handler Address Contains the address of the default

ISR handler.

Loading...

Loading...