LH79524/LH79525 User’s Guide Ethernet MAC Controller

Version 1.0 6-41

6.3.3.8 Deferred Transmission Frames (DEFTXFRM)

This is a 16-bit register containing the number of frames experiencing deferral due to

carrier sense being active on their first attempt at transmission. Frames involved in any col-

lision are not counted nor are frames that experienced a transmit underrun.

6.3.3.9 Late Collisions (LATECOL)

This is an 8-bit register containing the number of frames that experience a collision after

the slot time (512 bit times) has expired. A late collision is counted twice (both as a collision

and a late collision)

.

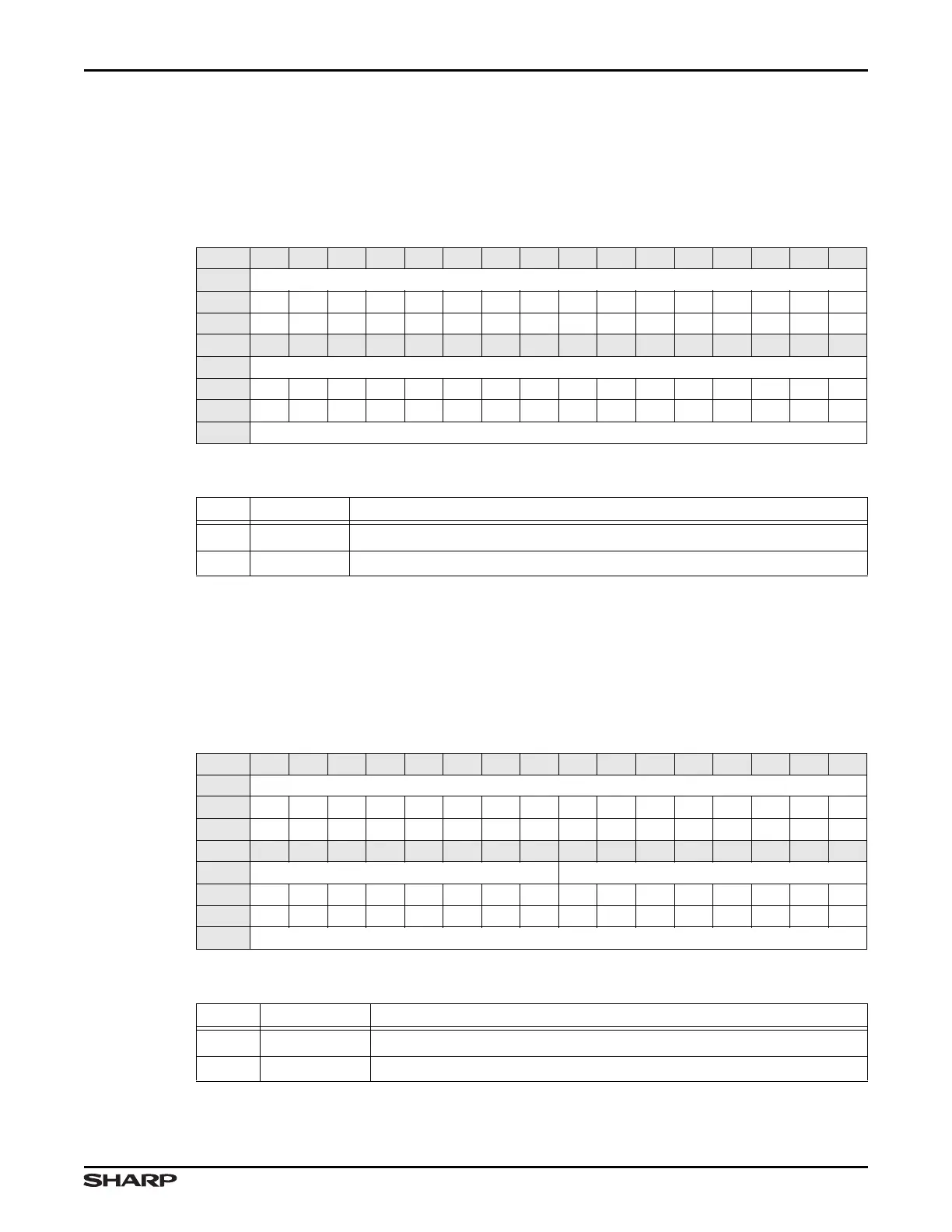

Table 6-48. DEFTXFRM Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD DEFTXFRM

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x58

Table 6-49. DEFTXFRM Fields

BITS NAME FUNCTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:0 DEFTXFRM Deferred Transmission Frames Deferred transmission frames count.

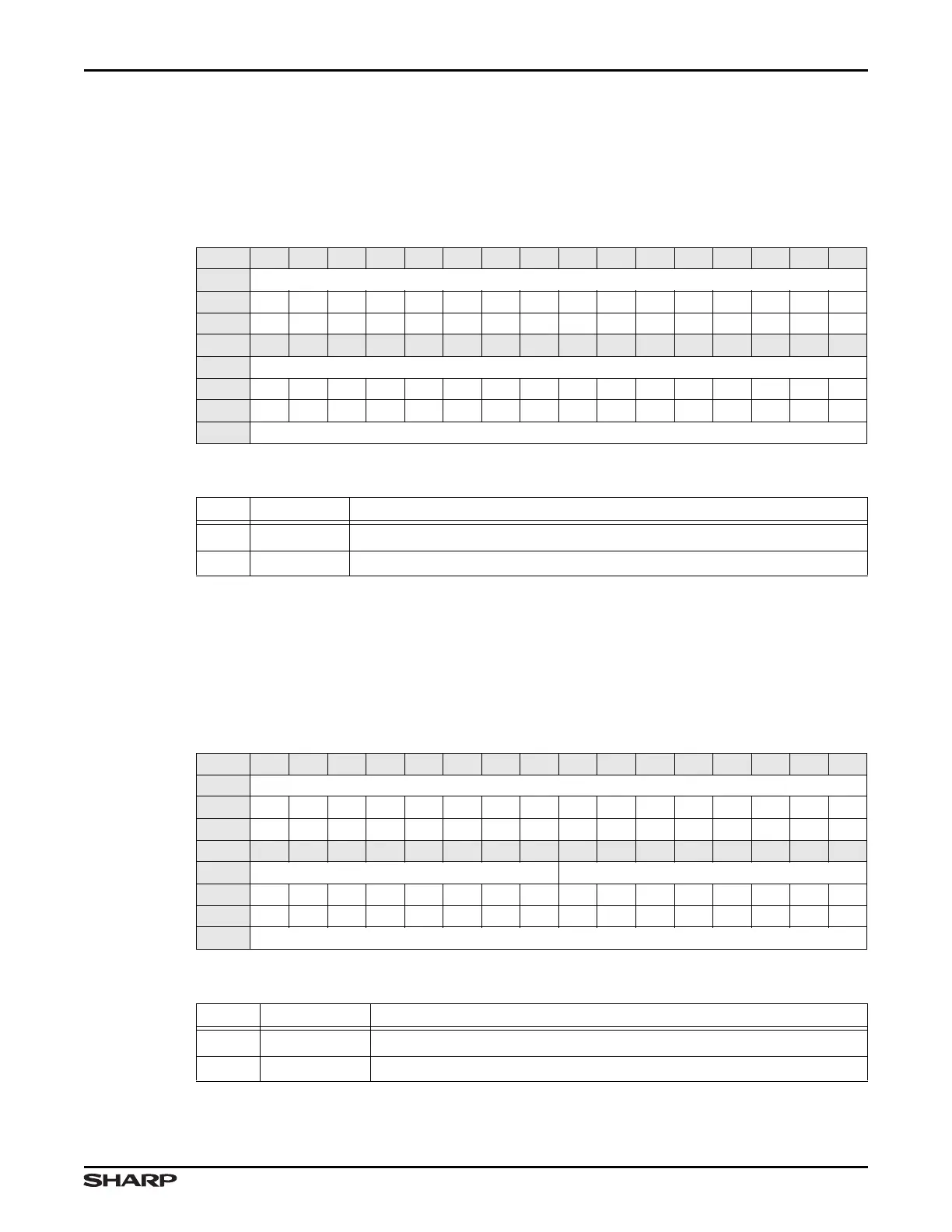

Table 6-50. LATECOL Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// LATECOL

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x5C

Table 6-51. LATECOL Fields

BITS NAME FUNCTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7:0 LATECOL Late Collisions Number of late collisions.

Loading...

Loading...