I

2

C Module LH79524/LH79525 User’s Guide

9-10 Version 1.0

9.2.2.5 I

2

C Clock High Time Register (ICHCNT)

The ICHCNT register allows programming the length of the serial clock HIGH time.

9.2.2.6 I

2

C Clock Low Time Register (ICLCNT)

The ICLCNT register allows programming the length of the serial clock LOW time.

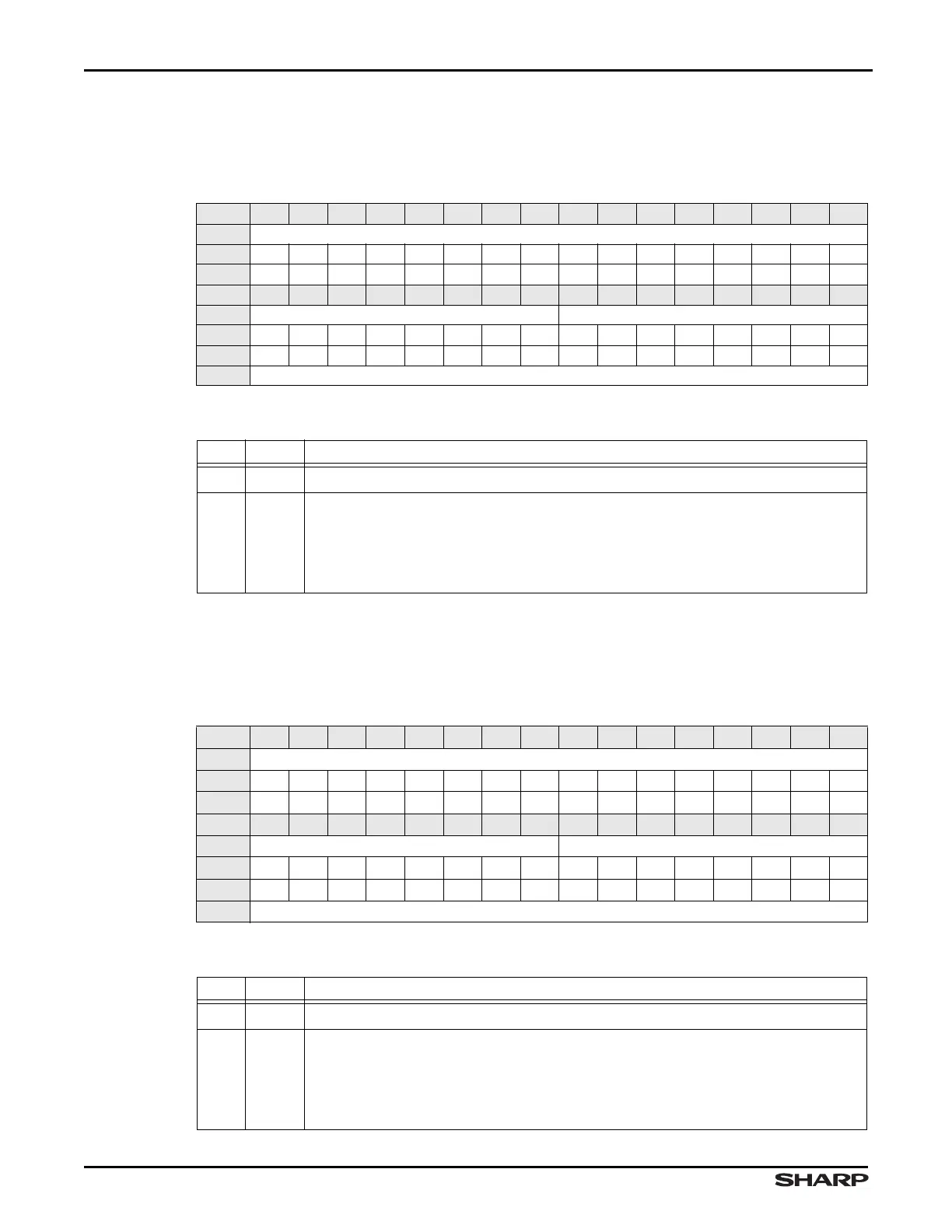

Table 9-12. ICHCNT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// HCNT

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC5000 + 0x10

Table 9-13. ICHCNT Fields

BITS NAME DESCRIPTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7:0 HCNT

High Count This field allows programming the SCL HIGH time, in HCLK

periods. The value is a hexadecimal number. The HIGH time is ICHCNT + 3

HCLK periods in 100 kbit/s mode, and ICHCNT + 4 HCLK cycles in 400 kbit/s

mode. The ICHCNT Register must be programmed before any I

2

C bus transac-

tion can take place to insure proper timing.

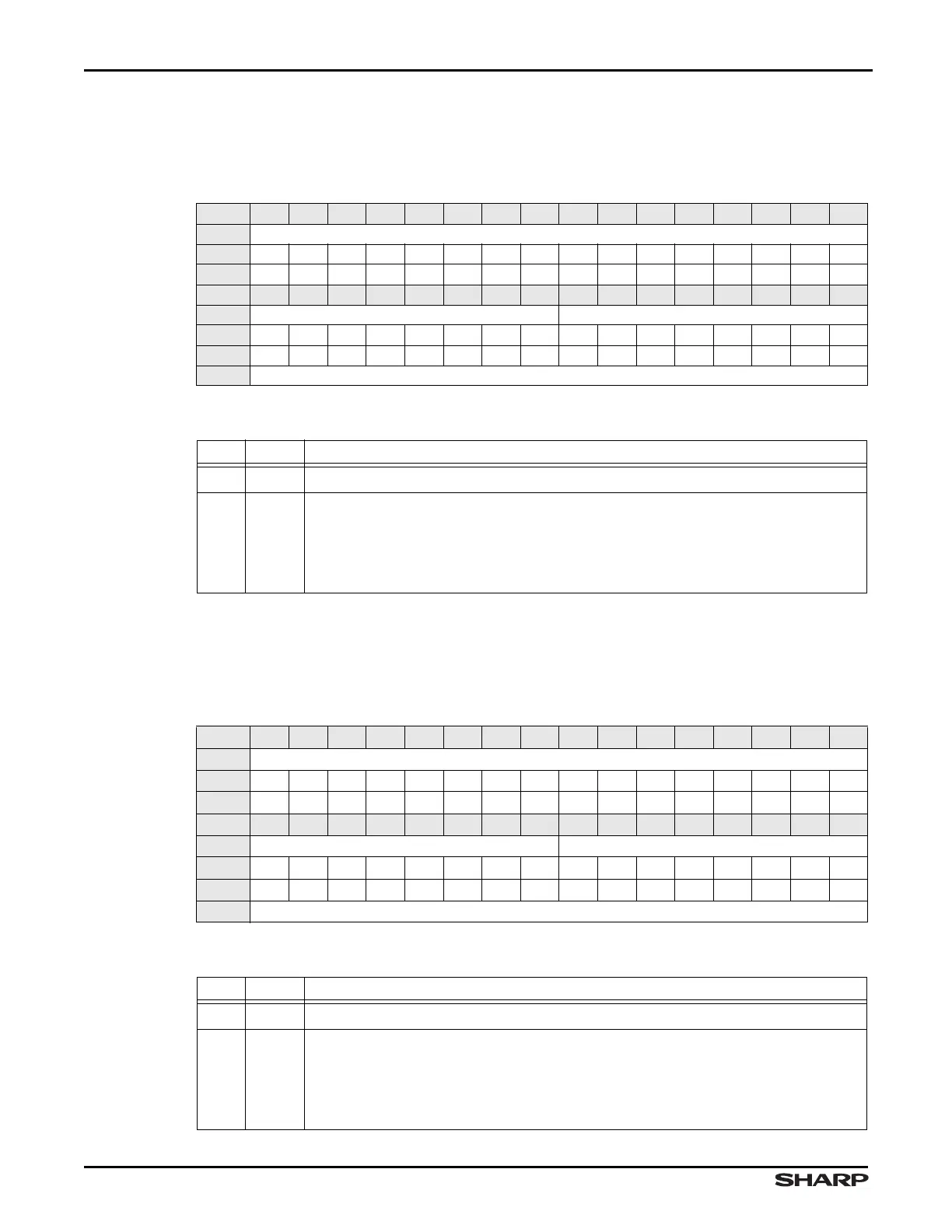

Table 9-14. ICLCNT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD /// LCNT

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW RW

ADDR 0xFFFC5000 + 0x14

Table 9-15. ICLCNT Fields

BITS NAME DESCRIPTION

31:8 /// Reserved Reading returns 0. Write the reset value.

7:0 LCNT

Low Count This register allows programming the SCL LOW time, in HCLK periods.

The value is a hexadecimal number. The LOW time is ICLCNT + 3 HCLK periods in

100 kbit/s mode, and ICLCNT + 4 HCLK cycles in 400 kbit/s mode. The ICLCNT Reg-

ister must be set before any I

2

C bus transaction takes place to insure proper timing.

Note that the value in this register must be at least 3 for proper I

2

C operation.

Loading...

Loading...