Boot Controller LH79524/LH79525 User’s Guide

3-10 Version 1.0

3.2.4 External Peripheral Mapping Register (EPM)

This register determines which chip selects will have burst accesses to their address

regions converted to a series of non-sequential transfers. The register provides individual

selectability for each of nCS0, nCS1, nCS2, and nCS3. At reset, accesses to all four chip

select regions have conversion enabled. This ensures that all external devices will be

accessible following reset.

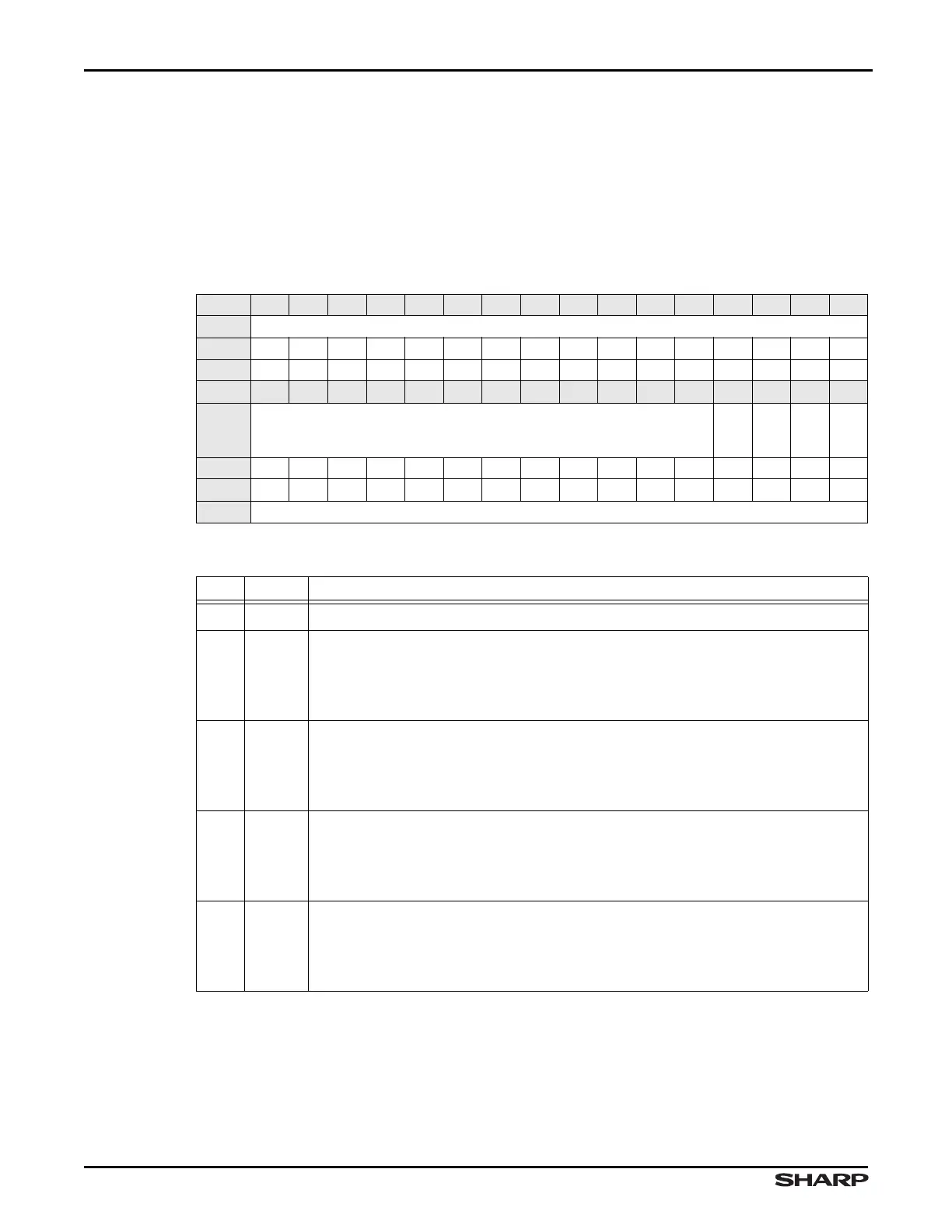

Table 3-12. EPM Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

CS3EP

CS2EP

CS1EP

CS0EP

RESET 0000000000001111

RW RO RO RO RO RO RO RO RO RO RO RO RO RW RW RW RW

ADDR 0xFFFE6000 + 0x08

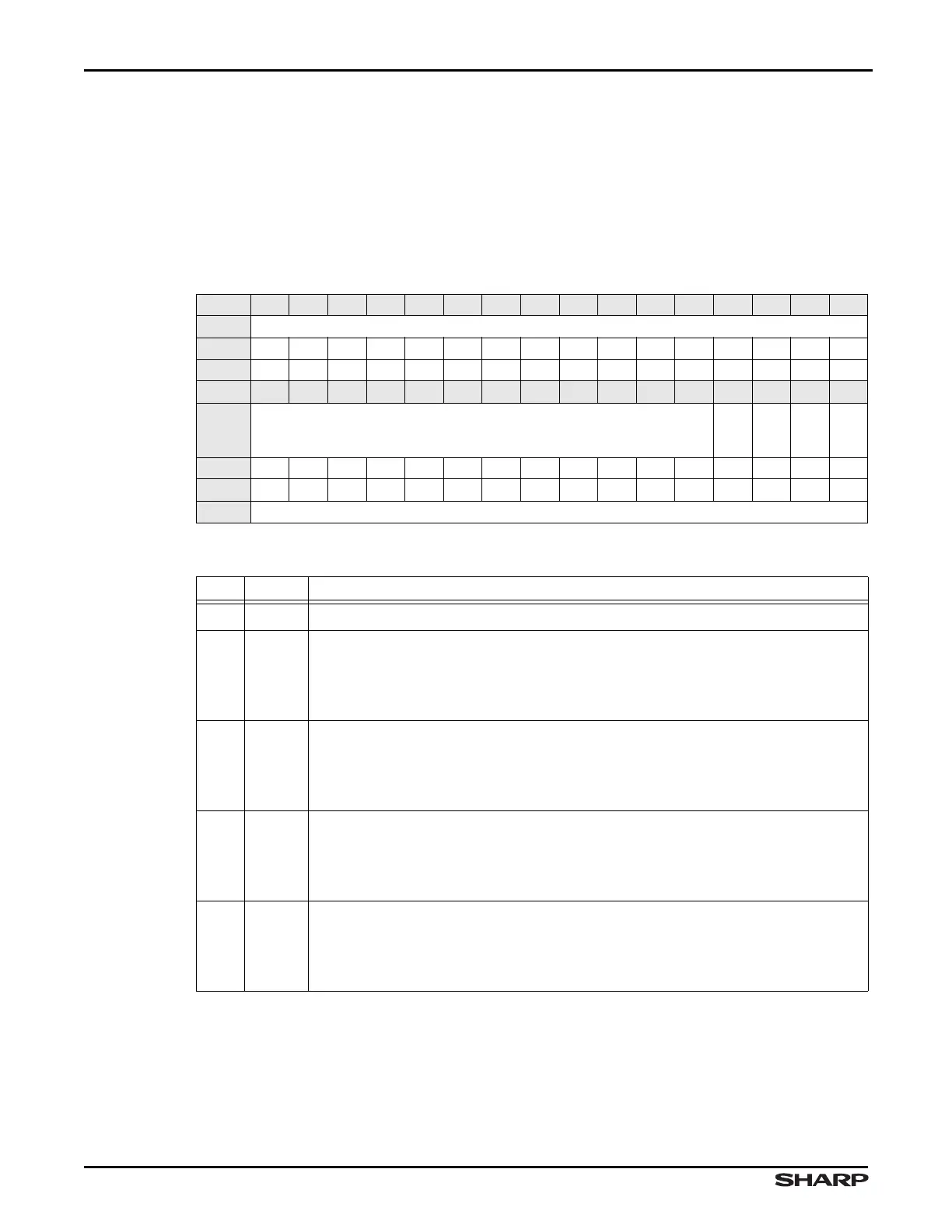

Table 3-13. EPM Fields

BITS NAME DESCRIPTION

31:4 /// Reserved Reading returns 0. Write the reset value.

3 CS3EP

nCS3 Configured for External Peripherals

1 = All burst accesses to nCS3 are converted to a series of non-sequential single

transfers.

0 = Accesses to nCS3 are unaltered.

2 CS2EP

nCS2 Configured for External Peripherals

1 = All burst accesses to nCS2 are converted to a series of non-sequential single

transfers.

0 = Accesses to nCS2 are unaltered.

1 CS1EP

nCS1 Configured for External Peripherals

1 = All burst accesses to nCS1 are converted to a series of non-sequential single

transfers.

0 = Accesses to nCS1 are unaltered.

0 CS0EP

nCS0 Configured for External Peripherals

1 = All burst accesses to nCS0 are converted to a series of non-sequential single

transfers.

0 = Accesses to nCS0 are unaltered.

Loading...

Loading...