Vectored Interrupt Controller LH79524/LH79525 User’s Guide

18-8 Version 1.0

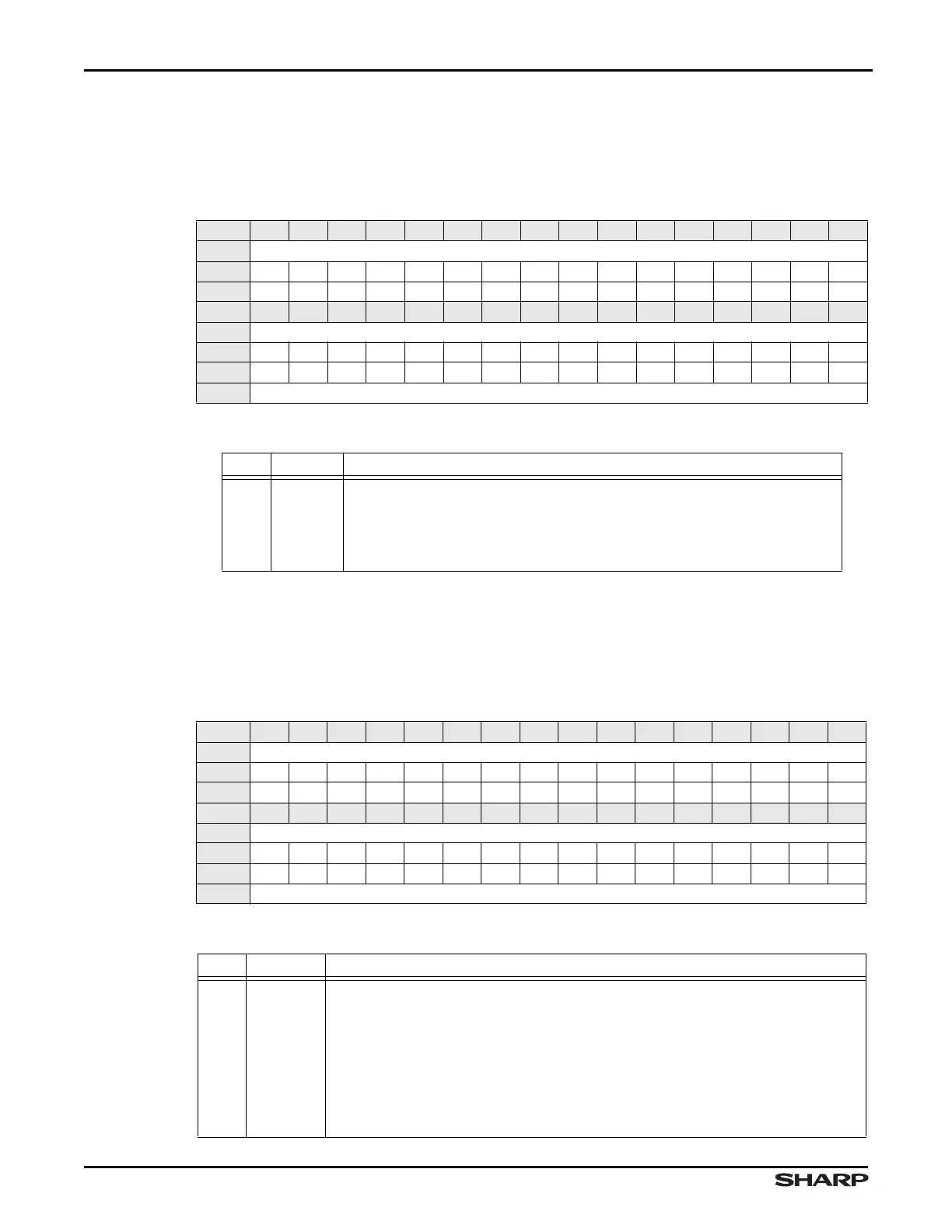

18.2.2.4 Interrupt Select Register (INTSELECT)

This register selects whether the corresponding interrupt source generates an FIQ or an

IRQ interrupt. Bits [31:0] correspond to the interrupt number in Table 18-1

.

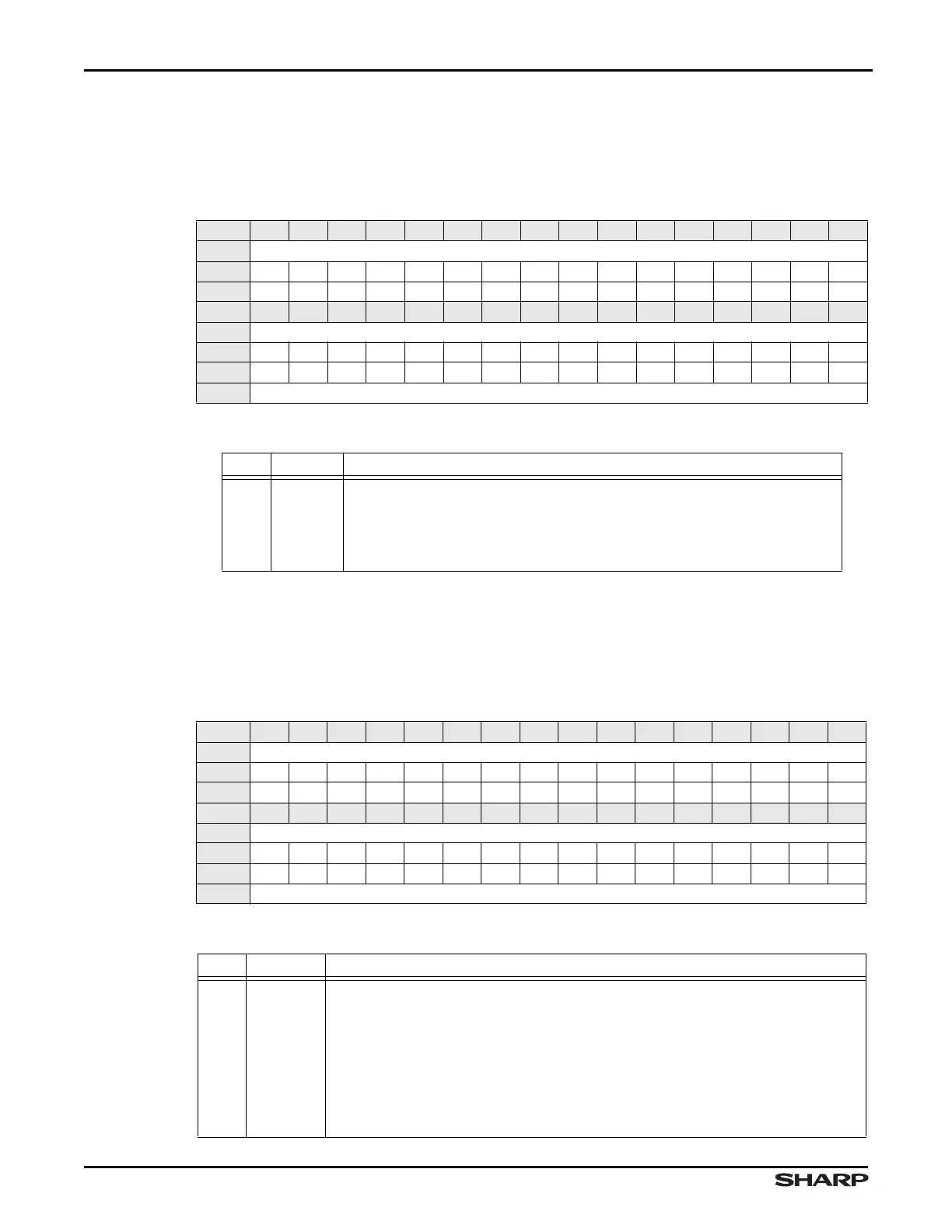

18.2.2.5 Interrupt Enable Register (INTENABLE)

The bits in this register allow software to individually enable and disable interrupts. Bits

[31:0] correspond to the interrupt number in Table 18-1

.

Table 18-9. INTSELECT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD IntSelect

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD IntSelect

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFFF000 + 0x00C

Table 18-10. INTSELECT Fields

BITS NAME DESCRIPTION

31:0 IntSelect

Interrupt Type Selects the type of interrupt for the interrupt request.

For each bit:

1 = FIQ interrupt

0 = IRQ interrupt

Table 18-11. INTENABLE Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD IntEnable

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD IntEnable

RESET 0000000000000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFFF000 + 0x010

Table 18-12. INTENABLE Fields

BITS NAME DESCRIPTION

31:0 IntEnable

Interrupt Enable Following a System Reset, all interrupts are disabled.

Read, for each bit:

1 = Interrupt is enabled, allowing interrupt request to the core CPU

0 = Interrupt is disabled

Write, for each bit:

1 = Enable the corresponding interrupt

0 = Has no effect

Loading...

Loading...