LH79524/LH79525 User’s Guide Analog-to-Digital Converter/Brownout Detector

Version 1.0 2-15

2.2.2.4 Interrupt Mask Register (IM)

IM is the Interrupt Mask /Enable register. The active bits used in this register are Read/

Write and enable the interrupts. Software can read the status of the interrupt bits through

the IS Register, even if corresponding mask bits are set in this register. The Brown Out

enable is unique in that the Brown Out Interrupt can be programmed to be either an FIQ

or an IRQ. That programming is done in this register. The Interrupt Status (IS) and Masked

Interrupt Status (MIS) registers show only the status of the interrupt, not how it is config-

ured. Current configuration can be read from this register. Writing a 0 to an IM bit does not

clear the latched interrupt status in the IS register. The IS register is logically ANDed with

the IE register to create the contents of the Masked Interrupt Status (MIS) register.

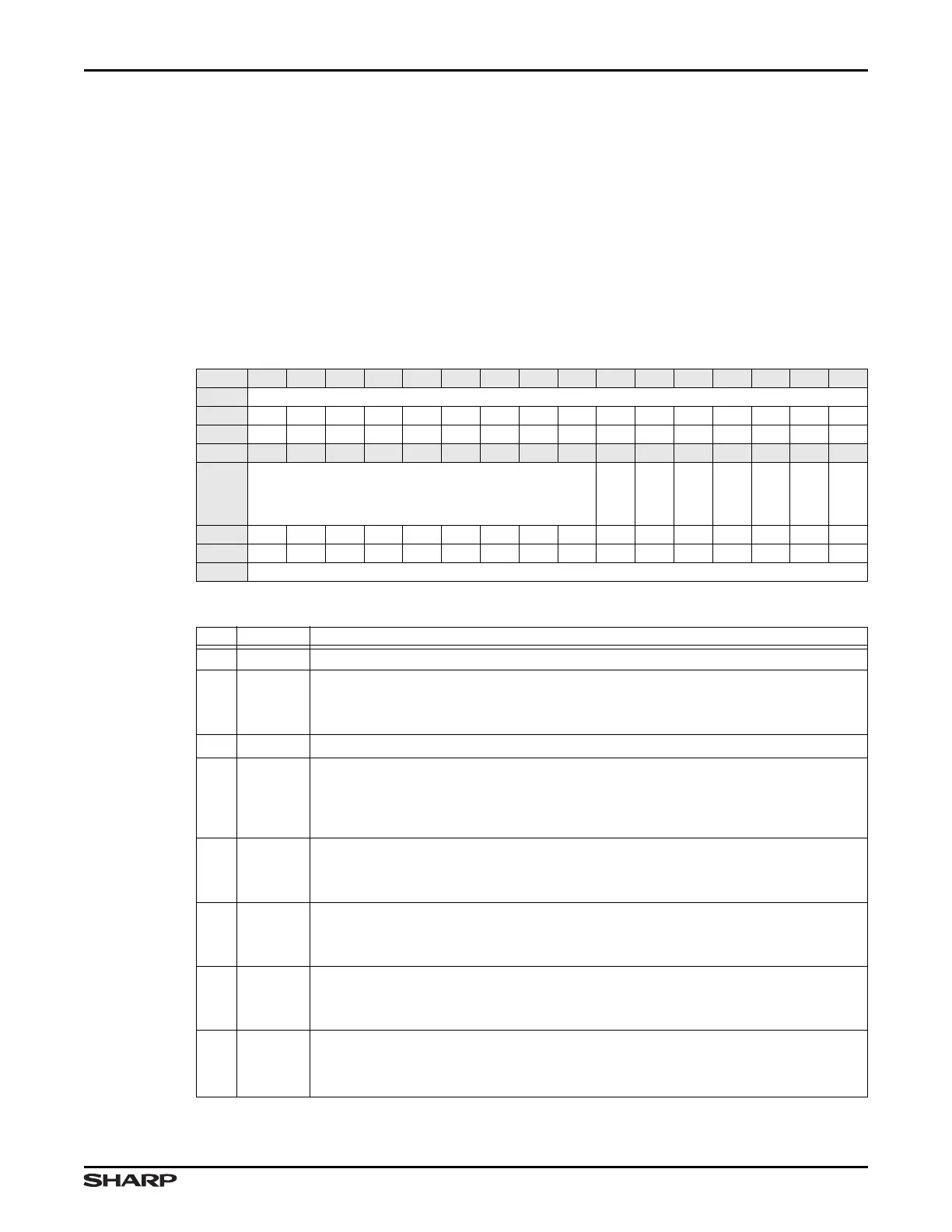

Table 2-9. IM Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

INTEN

///

BOIRQ

PMSK

EOSMSK

FWMSK

FOMSK

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RW RW RW RW RW RW RW

ADDR 0xFFFC3000 + 0x0C

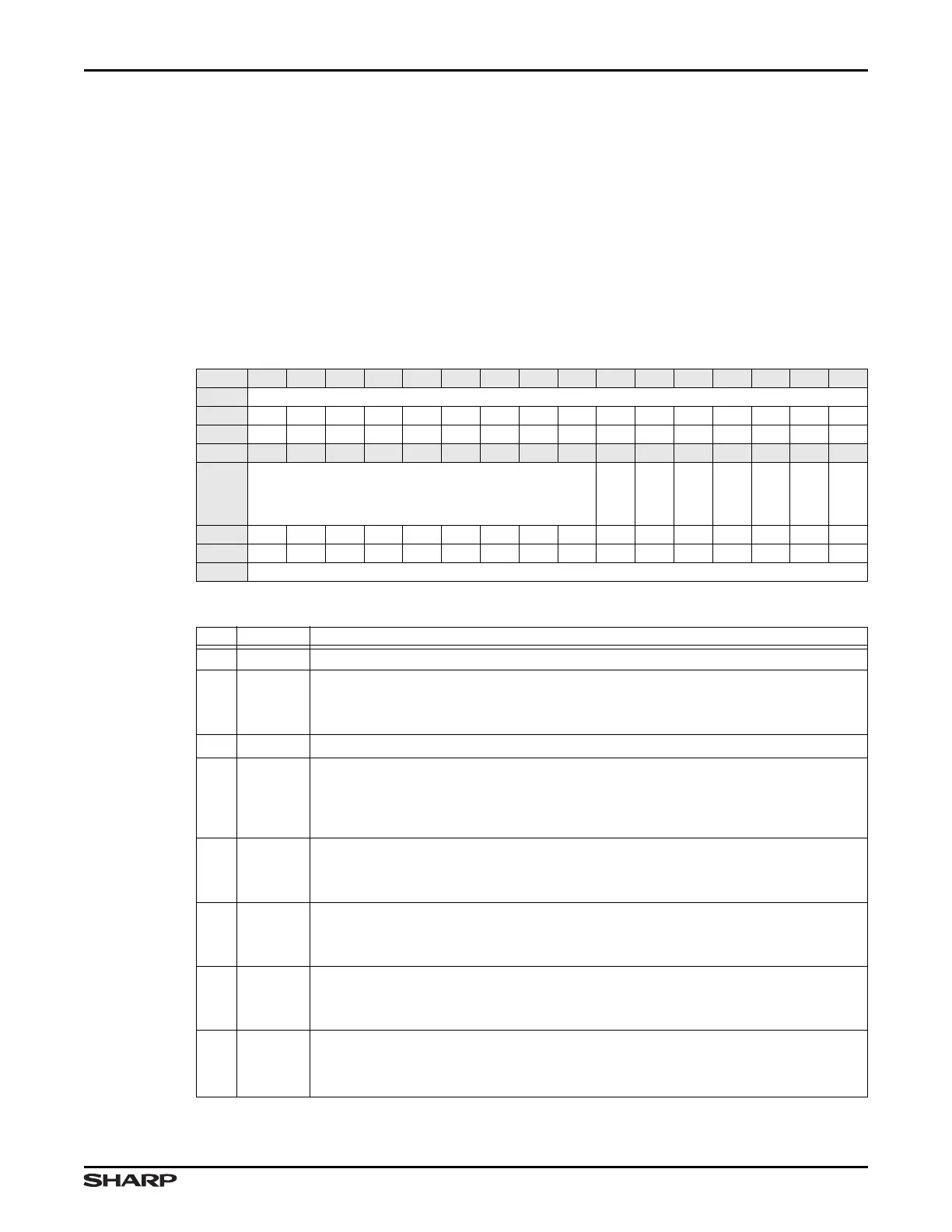

Table 2-10. IM Fields

BIT NAME DESCRIPTION

31:7 /// Reserved Reading returns 0. Write the reset value.

6 INTEN

Interrupt Enable

1 = Global IRQ interrupts enabled

0 = Global IRQ interrupts masked

5

/// Reserved Reading returns 0. Write the reset value.

4 BOIRQ

Brown Out IRQ Enable Enabling this bit allows the brownout detector to generate an

interrupt request as part of the combined TSCINTR input of the VIC.

1 = Enable Brown Out IRQ to VIC

0 = Disable Brown Out IRQ to VIC

3 PMSK

Pen IRQ Interrupt Enable

1 = Pen IRQ enabled

0 = Pen IRQ masked

2 EOSMSK

End-of-Sequence Interrupt Enable

1 = EOS IRQ enabled

0 = EOS IRQ masked

1 FWMSK

FIFO Watermark Interrupt Enable

1 = FIFO Watermark IRQ enabled

0 = FIFO Watermark IRQ masked

0 FOMSK

FIFO Overrun Interrupt Enable

1 = FIFO Overrun IRQ enabled

0 = FIFO Overrun IRQ masked

Loading...

Loading...