General Purpose Input/Output LH79524/LH79525 User’s Guide

8-2 Version 1.0

8.1.1.1 Multiplexing

All of the GPIO pins are multiplexed with one or more other functions. Selecting certain on-

chip peripherals removes the GPIO function from that pin. Configuration of these multi-

plexed pins is described in the I/O Configuration chapter.

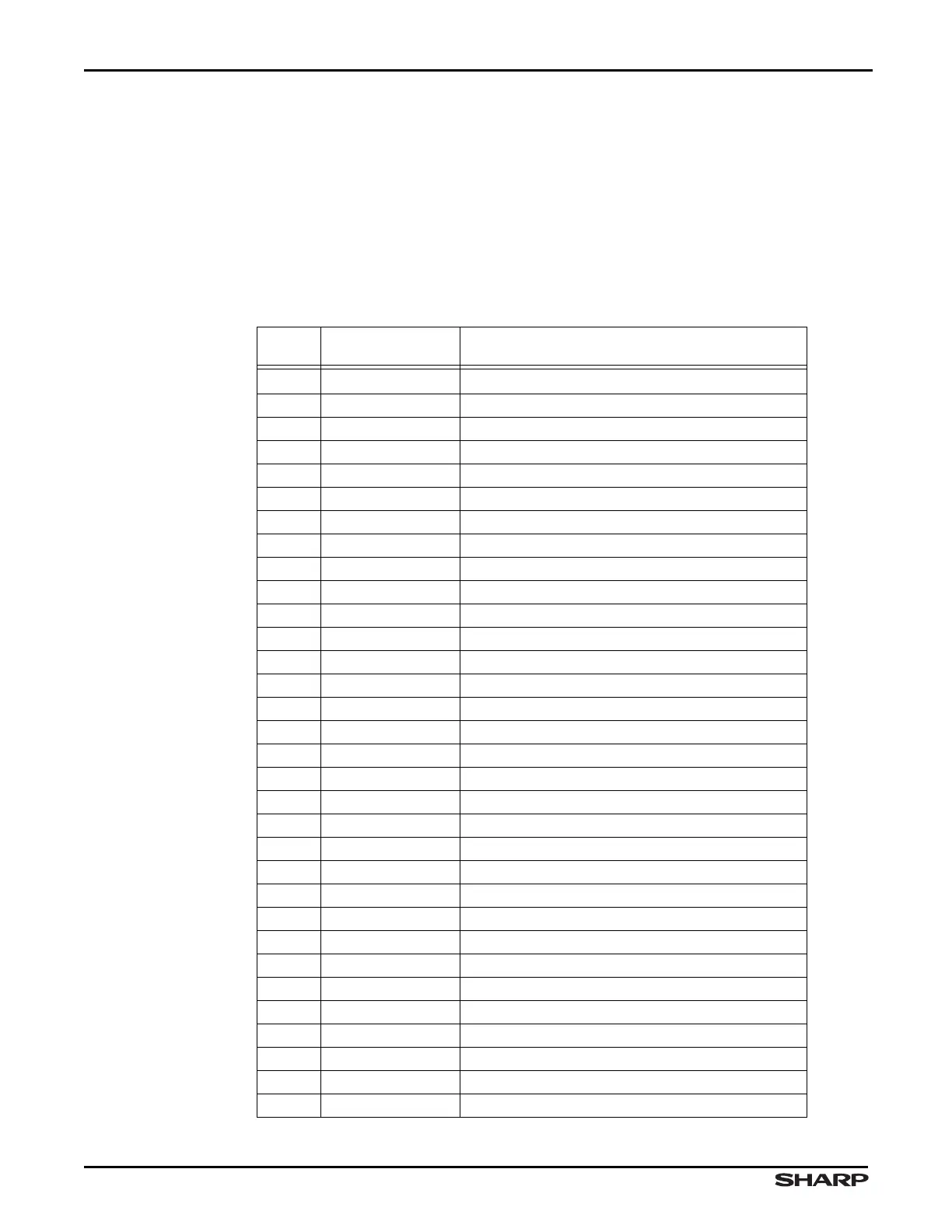

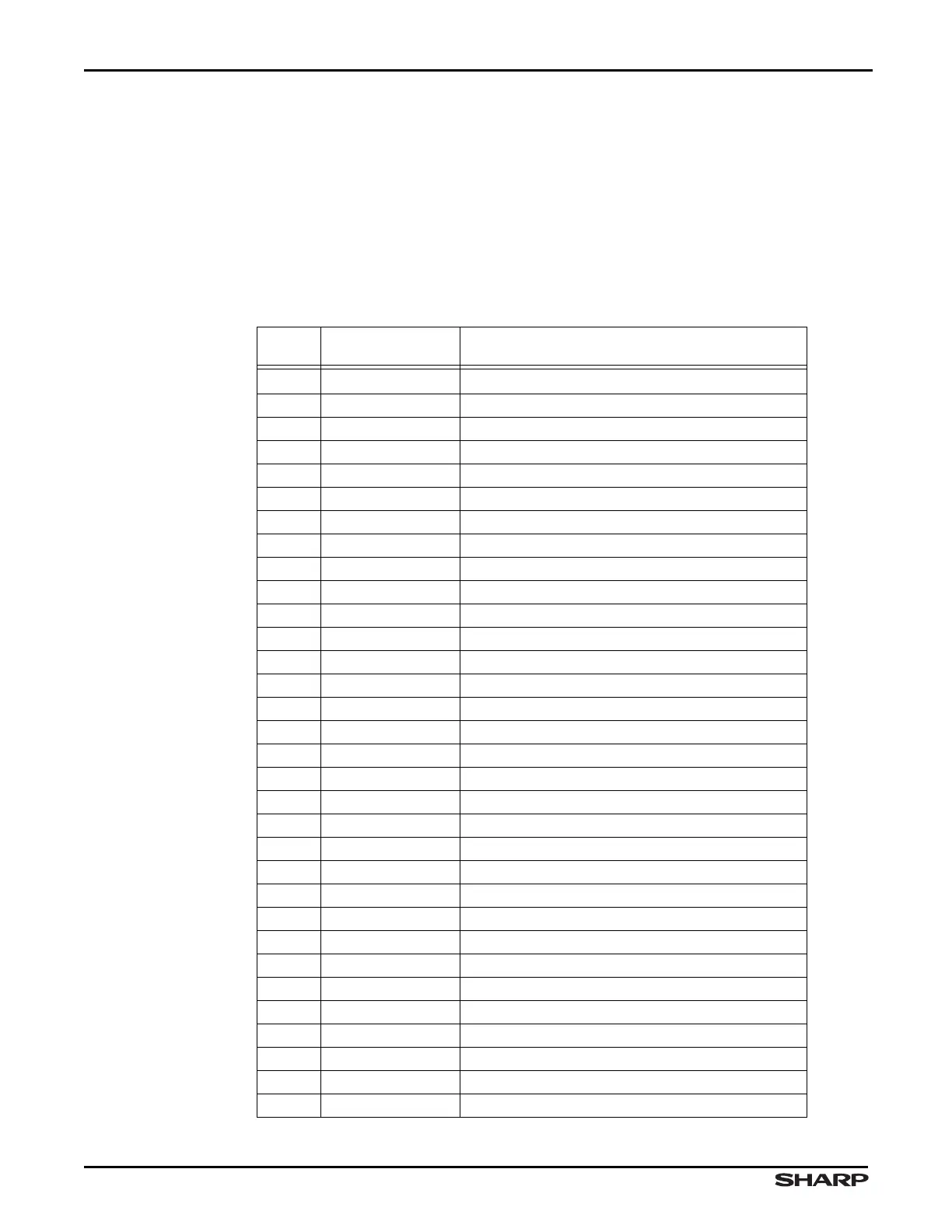

Table 8-2 and Table 8-3 show the multiplexed functions of each GPIO pin. In the case of

Port J and Port M, the reset function is not GPIO, hence those functions are listed in the

‘Multiplexed Function’ column.

Table 8-2. LH79524 GPIO Multiplexing

CABGA

NO.

AT RESET MULTIPLEXED FUNCTION(S)

N1 PA0 INT2/UARTRX2/UARTIRRX2

M2 PA1 INT3/UARTTX2/UARTIRTX2

L3 PA2 CTCAP0A/CTCMP0A

M1 PA3 CTCAP0B/CTCMP0B

L2 PA4 CTCAP1A/CTCMP1A

L1 PA5 CTCAP1B/CTCMP1B

K3 PA6 CTCAP2A/CTCMP2A/SDA

K2 PA7 CTCAP2B/CTCMP2B/SCL

R2 PB0 nDACK/nUARTCTS0

R1 PB1 DREQ/nUARTRTS0

P2 PB2 SSPFRM/I2SWS

N3 PB3 SSPCLK/I2SCLK

M4 PB4 SSPRX/I2SRXD/UARTRX1/UARTIRRX1

P1 PB5 SSPTX/I2STXD/UARTTX1/UARTIRTX1

N2 PB6 INT0/UARTRX0/UARTIRRX0

M3 PB7 INT1/UARTTX0/UARTIRTX0

N7 PC0 A16

R6 PC1 A17

T5 PC2 A18

P6 PC3 A19

R5 PC4 A20

T4 PC5 A21

P5 PC6 A22/nFWE

R4 PC7 A23/nFRE

P15 PD0 D8

P14 PD1 D9

N13 PD2 D10

T15 PD3 D11

N12 PD4 D12

T14 PD5 D13

P12 PD6 D14

T13 PD7 D15

Loading...

Loading...