LH79524/LH79525 User’s Guide Boot Controller

Version 1.0 3-7

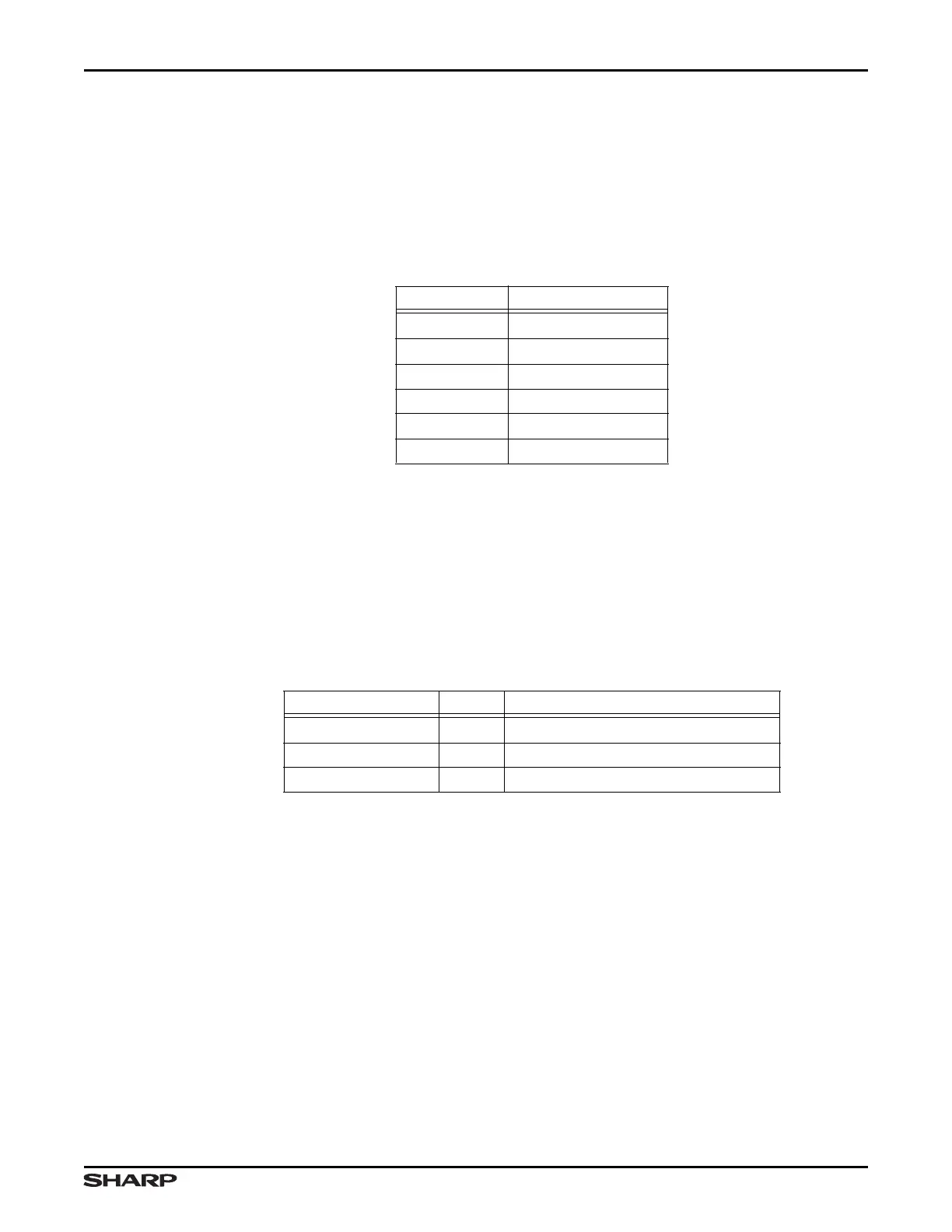

3.1.4 Booting from UART

Another boot option is to boot using UART0. The transfer protocol implementation is

XMODEM with 128-byte packets. All UART0 parameters are summarized in Table 3-6.

The Boot Controller automatically handles initialization and setup of UART0; the source of

the boot code must be compatible with the parameters in the table.

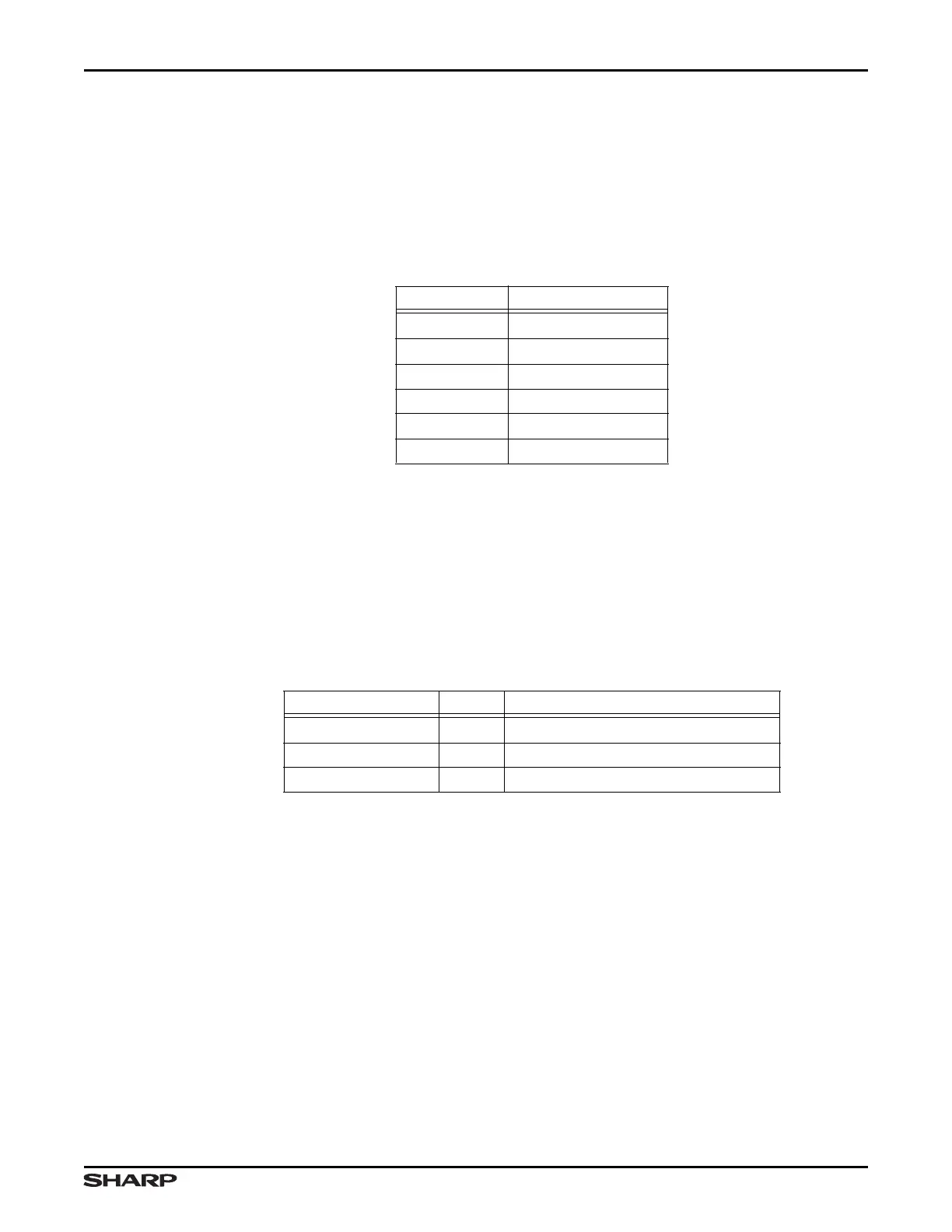

3.2 Register Reference

This section provides the Boot Controller register memory mapping and bit fields.

3.2.1 Memory Map

The base address for the Boot Controller is 0xFFFE6000. Table 3-7 summarizes the Boot

Controller registers.

Table 3-6. UART0 Boot Parameters

PARAMETER VALUE

Protocol XMODEM Checksum

Bit Rate 115 kbps

Data Bits 8

Parity None

Stop Bits 1

Packet Size 128 bytes

Table 3-7. Boot Controller Register Summary

ADDRESS OFFSET NAME DESCRIPTION

0x00 PBC Power-up Boot Configuration Register

0x04 CS1OV nCS1 Override Register

0x08 EPM External Peripheral Mapping Register

Loading...

Loading...