LH79524/LH79525 User’s Guide External Memory Controller

Version 1.0 7-15

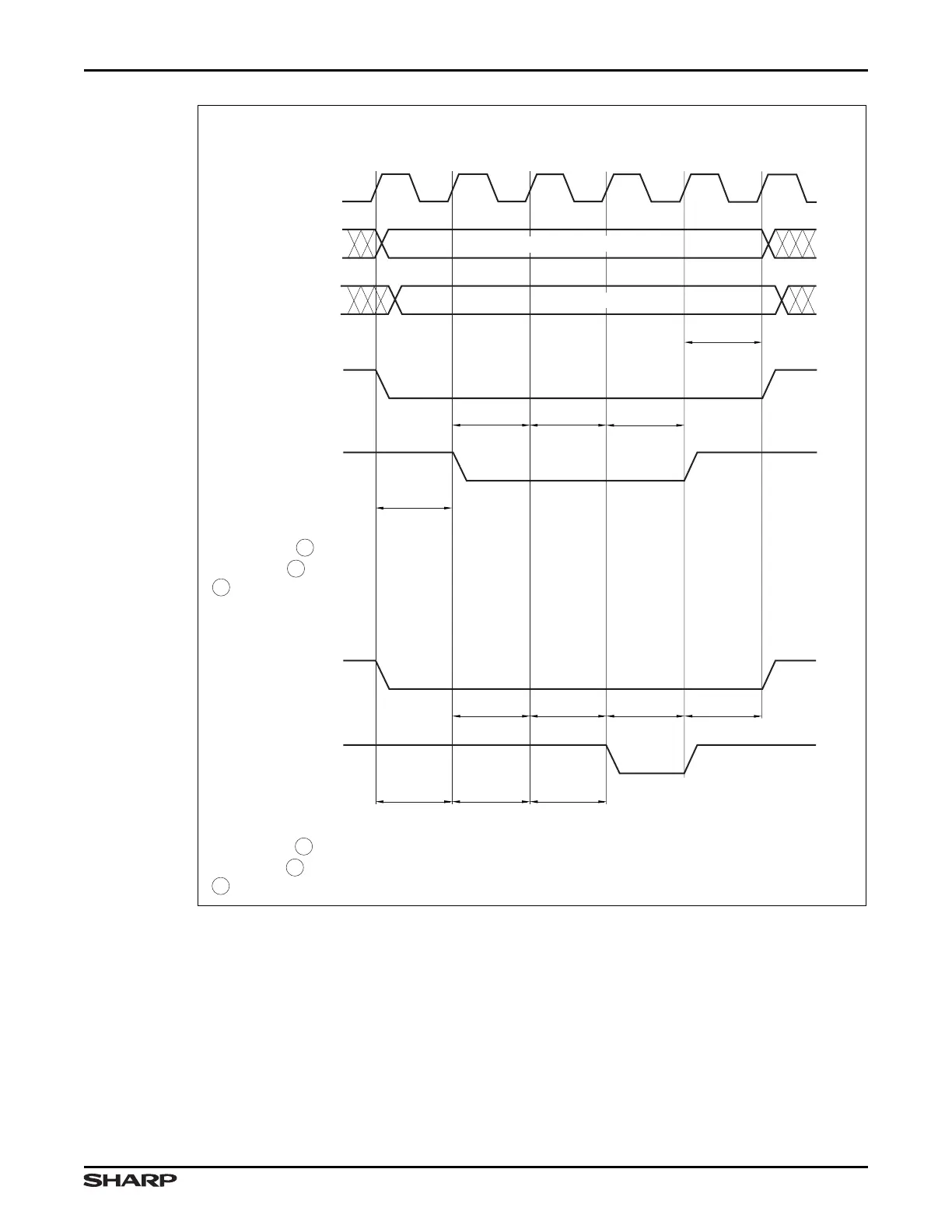

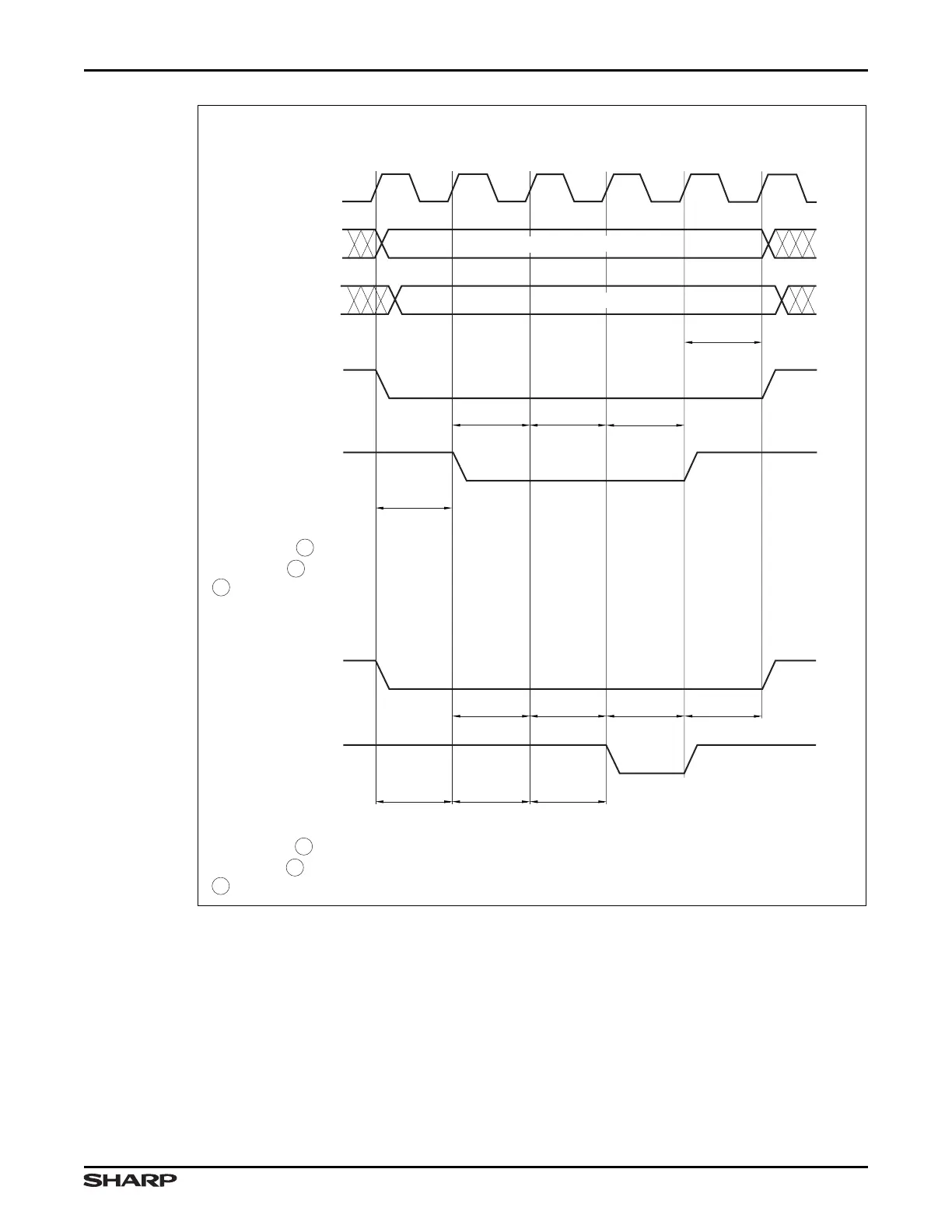

In Timing B, SWAITWENx (‘A’) = 0x2, and SWAITWRx (‘B’) = 0x2. As always, nCSx pre-

cedes nWE (nBLEx) by one HCLK period (A0). But instead of asserting at the end of A0,

assertion is delayed by A1 and A2. However, according to the Write cycle equation, those

terms do not delay the total cycle. As shown in the Figure, they are coincident with B0 and

B1. The nWE (nBLEx) signal then asserts at the conclusion of A2 and deasserts at the con-

clusion of B2. Obviously, if SWAITWENx

> SWAITWRx, no nWE (nBLEx) would exist. As

with Reads, multiple register values produce the same number of wait states. For Write

transactions, only the contents of SWAITWRx specify the number of wait states.

Figure 7-13. Static Write Transaction with Two Wait States

HCLK

A[23:0]

VALID ADDRESS

LH79525-11

NOTES:

With Register Programming:

SWAITWENx = A = 0x2

SWAITWRx = B = 0x2

C = Address hold

C

D[31:0]

nCSx

nWE or nBLEx

nCSx

nWE or nBLEx

VALID DATA

C

B0

A0

B1 B2

B0

B1 B2

A0

A1

A2

NOTES:

With Register Programming:

SWAITWENx = A = 0x0

SWAITWRx = B = 0x2

C = Address hold

TIMING A

TIMING B

Loading...

Loading...