LH79524/LH79525 User’s Guide Ethernet MAC Controller

Version 1.0 6-51

6.3.4.5 Specific Address 2 Bottom (SPECAD2BOT)

This register contains the least-significant bits of the destination address (bits [31:0]). Bit

zero indicates whether the address is multicast or unicast and corresponds to the least

significant bit of the first byte received.

6.3.4.6 Specific Address 2 Top (SPECAD2TOP)

This register contains the most-significant bits of the destination address (bits [47:32]).

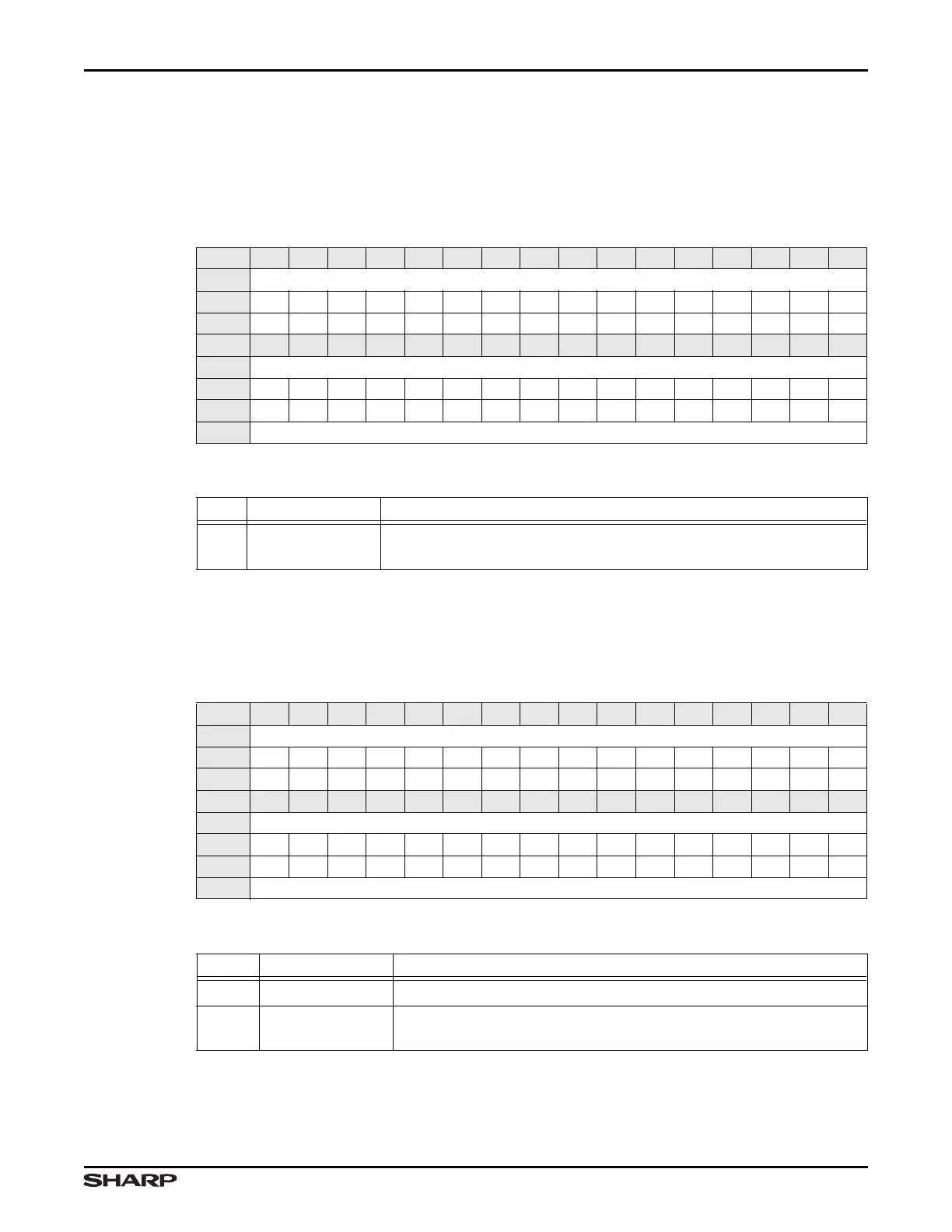

Table 6-84. SPECAD2BOT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD SPECAD2BOT

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD SPECAD2BOT

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0xA0

Table 6-85. SPECAD2BOT Fields

BITS NAME FUNCTION

31:0 SPECAD2BOT

Least Significant Destination Address Bits Least significant bits

of the destination address.

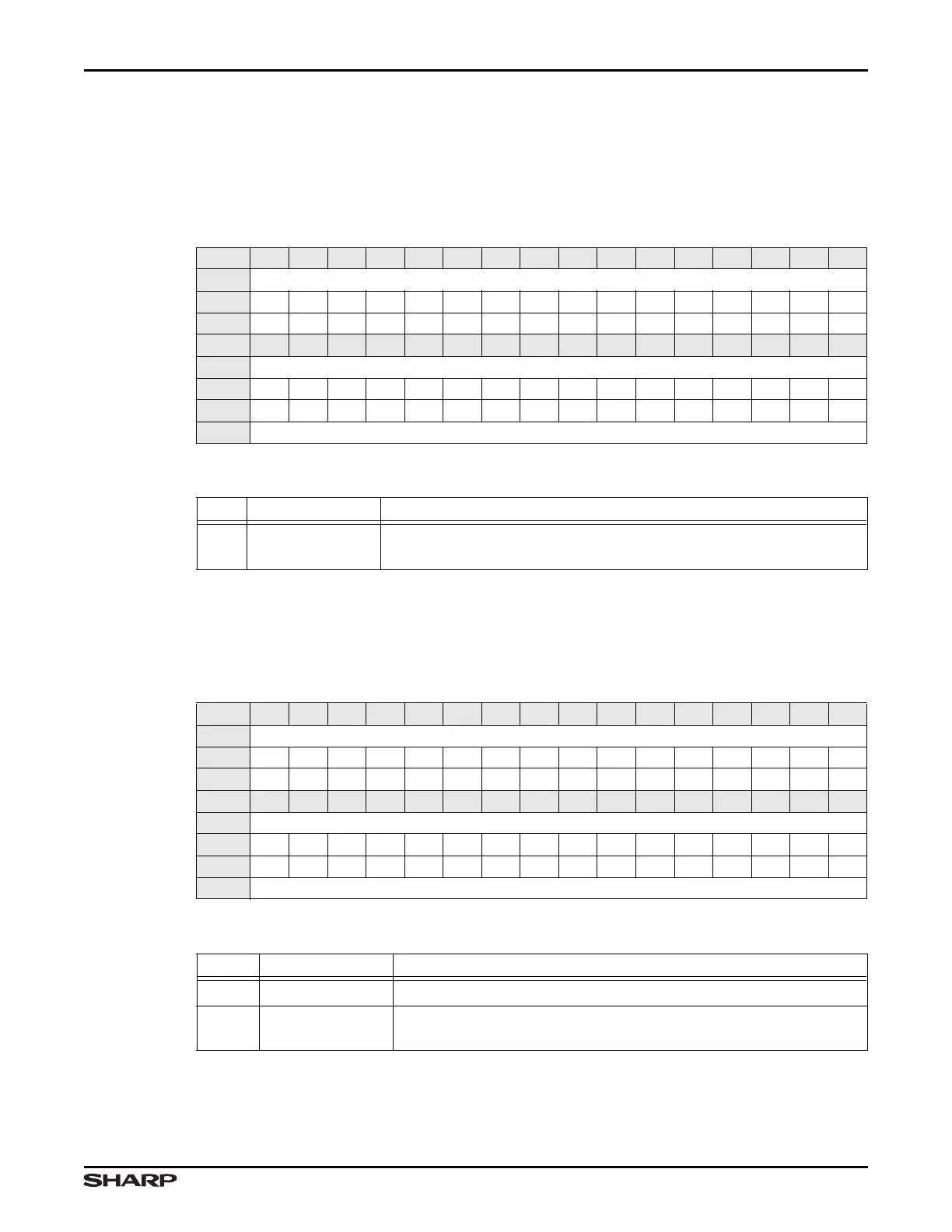

Table 6-86. SPECAD2TOP Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

TYPE RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD SPECAD2TOP

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0xA4

Table 6-87. SPECAD2TOP Fields

BITS NAME FUNCTION

31:16 /// Reserved Reading returns 0. Write the reset value.

15:0 SPECAD2TOP

Most Significant Destination Address Bits The most significant

bits of the destination address.

Loading...

Loading...