LH79524/LH79525 User’s Guide Real Time Clock

Version 1.0 12-5

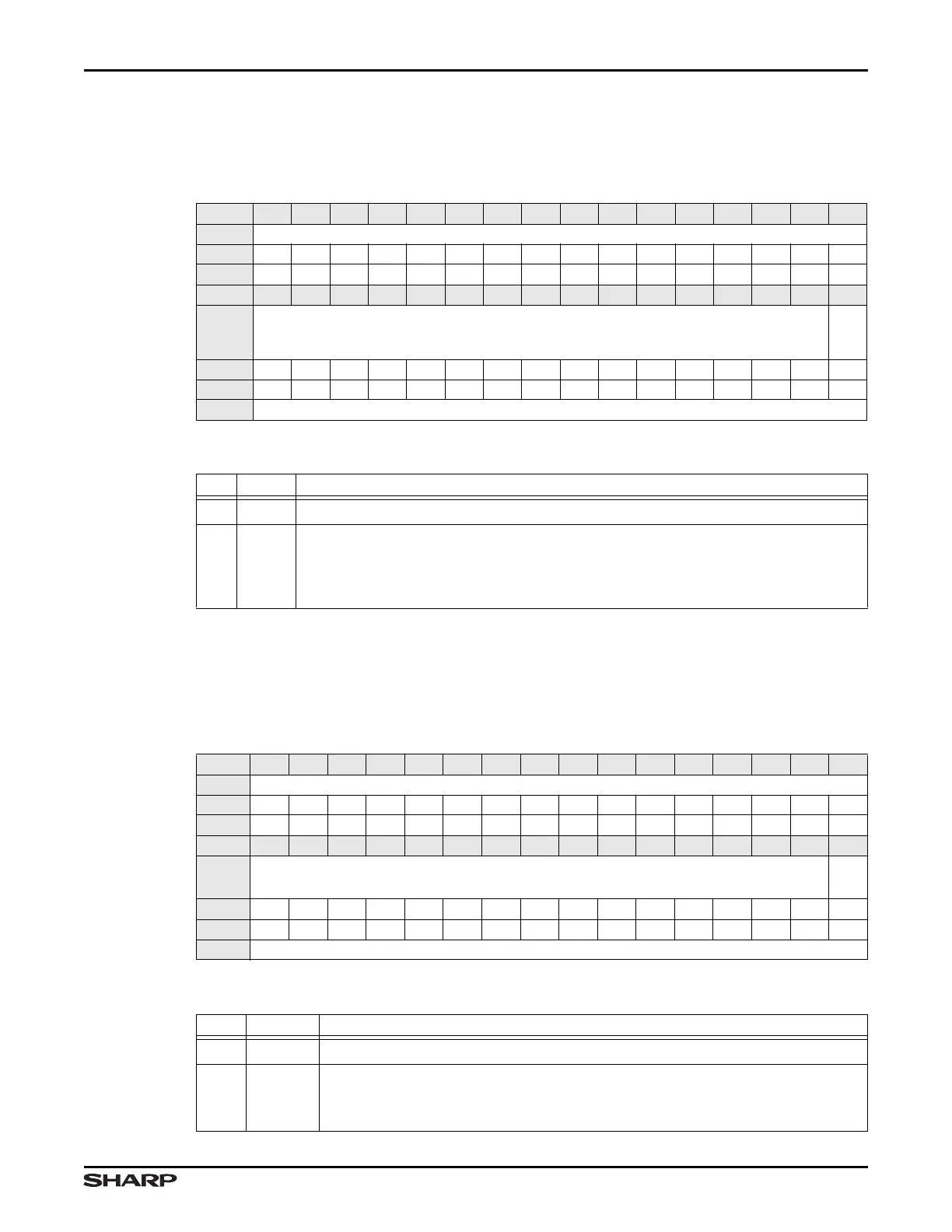

12.2.2.4 Control Register (CR)

CR allows software to enable the RTC and determine its operational status.

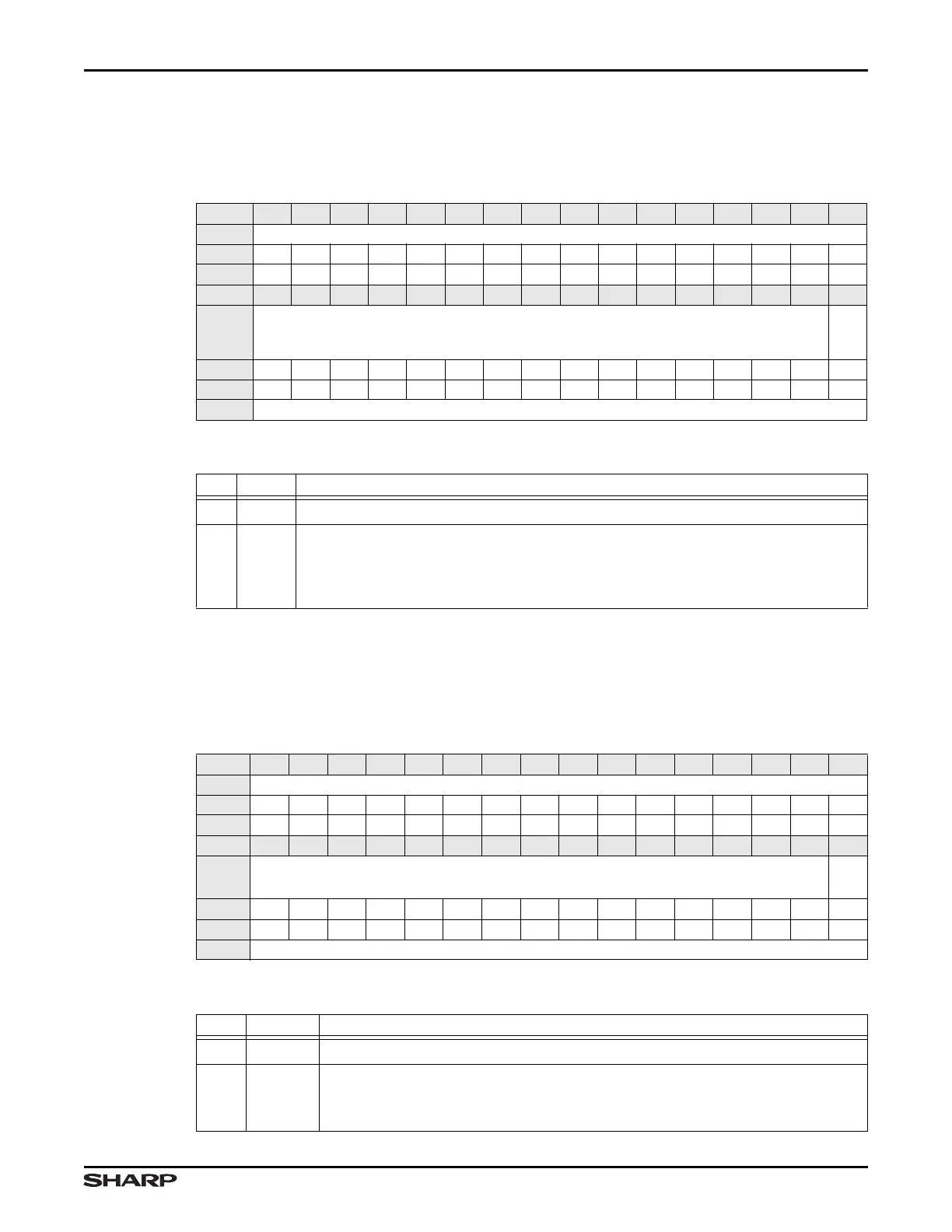

12.2.2.5 Interrupt Mask Set or Clear Register (IMSC)

IMSC controls the masking of the interrupt generated by the RTC. Reading this register

returns the current mask value of the RTC Interrupt.

Table 12-8. CR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

START

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RW

ADDR 0xFFFE0000 + 0x0C

Table 12-9. CR Fields

BIT NAME DESCRIPTION

31:1 /// Reserved Unpredictable values when read. Write the reset value.

0START

RTC Start The RTC can be enabled by writing a 1 to this bit. Once enabled, any writes to

this bit have no effect on the RTC until a system reset. Reading returns the status of the RTC.

1 = RTC enabled

0 = RTC disabled (read only)

Table 12-10. IMSC Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

IMSC

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RW

ADDR 0xFFFE0000 + 0x10

Table 12-11. IMSC Fields

BITS NAME DESCRIPTION

31:1 /// Reserved Reading returns 0. Values written cannot be read.

0IMSC

Interrupt Mask Set or Clear

1 = Interrupts unmasked, asserted to VIC when generated

0 = Interrupts masked and not asserted to the VIC

Loading...

Loading...