LH79524/LH79525 User’s Guide Ethernet MAC Controller

Version 1.0 6-35

6.3.2.12 PHY Maintenance Register (PHYMAINT)

This register enables the EMAC to communicate with a PHY by means of the MDIO inter-

face. It is used during auto negotiation to ensure that the EMAC and the PHY are config-

ured for the same speed and duplex configuration.

The PHY maintenance register is implemented as a shift register. Writing to the

register starts a shift operation, which is signalled as complete when bit two is set in the

NETSTATUS register, about 2,000 HCLK cycles later. An interrupt is also generated.

During this time, the MSB of the register is output on the ETHERMDIO pin and the LSB

updated from the ETHERMDIO pin with each ETHERMDC cycle. This causes transmis-

sion of a PHY management frame on ETHERMDIO. See Section 22.2.4.5 of the IEEE

802.3 standard.

Reading during the shift operation will return the current contents of the shift register. At

the end of management operation, the bits will have shifted back to their original locations.

For a read operation, the data bits will be updated with data read from the PHY.

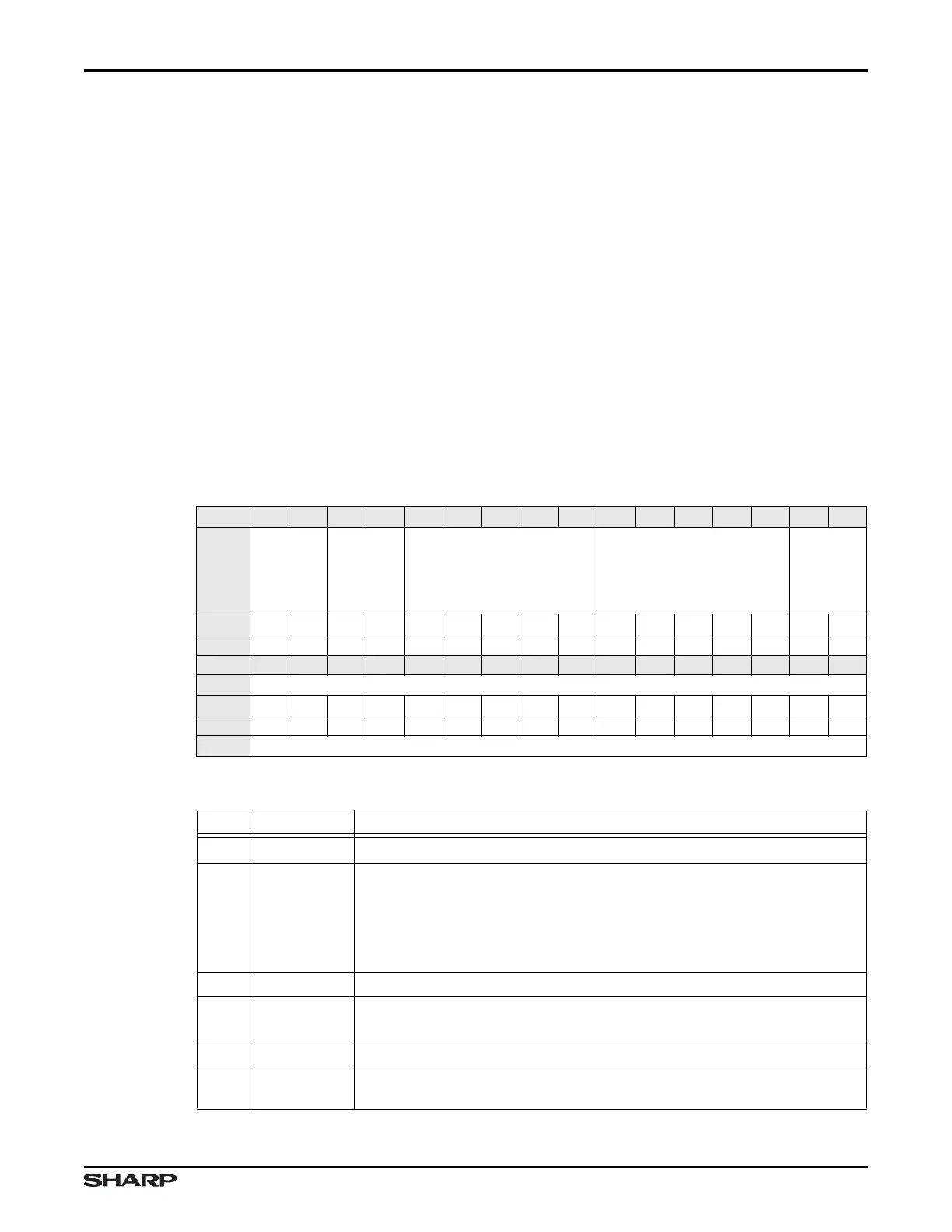

Table 6-28. PHYMAINT Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD

STARTFRM

OPERATION

PHYADDR REGADDR ///

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD PHYRDWR

RESET 0000000000000000

TYPE RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR 0xFFFC7000 + 0x34

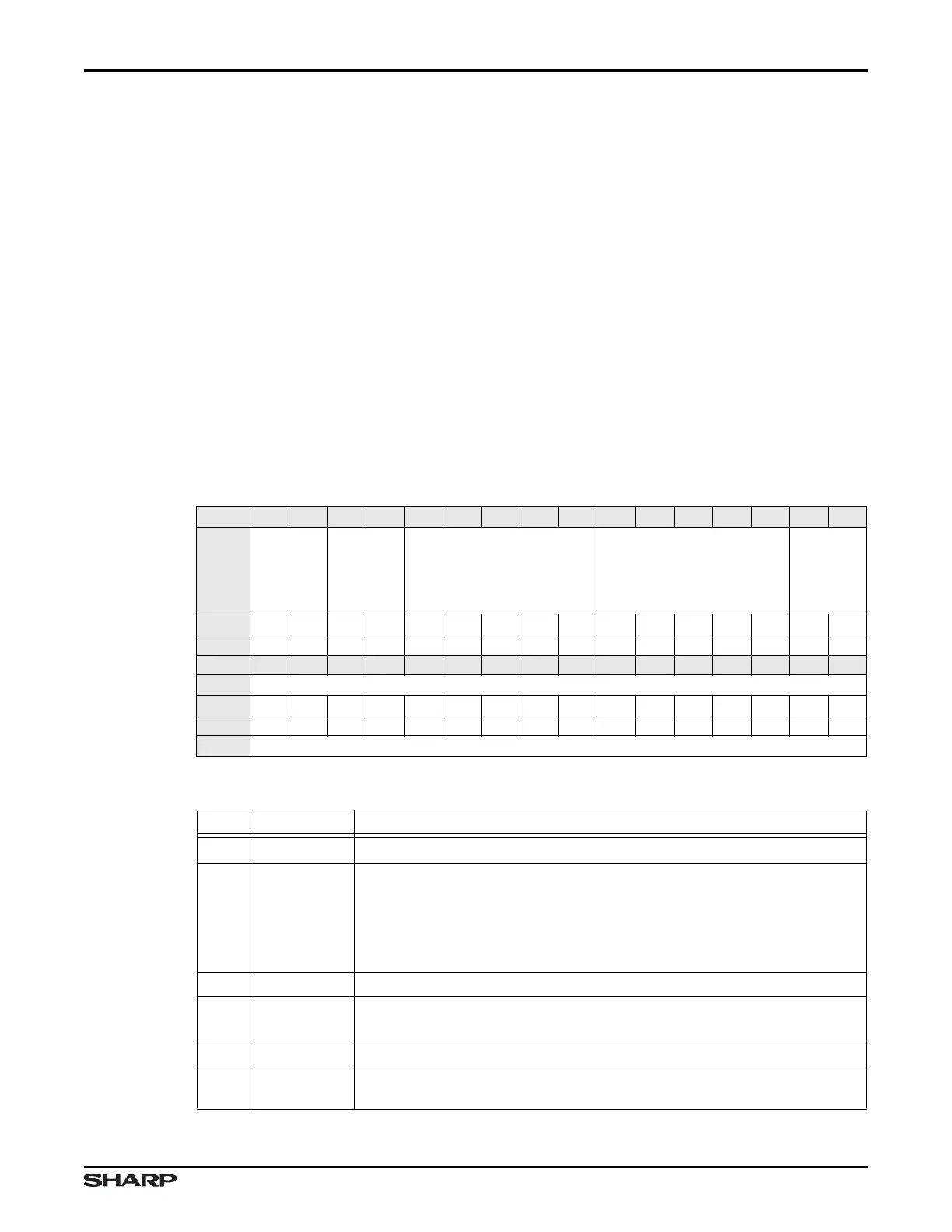

Table 6-29. PHYMAINT Fields

BITS NAME FUNCTION

31:30 STARTFRM Start Of Frame Must be written 0b01 for a valid frame.

29:28 OPERATION

Operation

00 = Invalid

01 = Write

10 = Read

11 = Invalid

27:23 PHYADDR Phy Address The PHY address is written to this field.

22:18 REGADDR

Register Address Specifies the address of the register in the PHY

to access.

17:16 /// Must be written with 0b10. Reads the value written.

15:0 PHYRDWR

PHY Read or Write Data The data to be written to the PHY is contained in

these two bytes. For a read, this contains the two bytes read from the PHY.

Loading...

Loading...