UARTs LH79524/LH79525 User’s Guide

16-26 Version 1.0

16.3.2.13 Interrupt Clear Register (UARTICR)

UARTICR is the Interrupt Clear Register. The active bits used in this register are Write

Only. On a write of 1, the corresponding interrupt is cleared. A write of 0 has no effect.

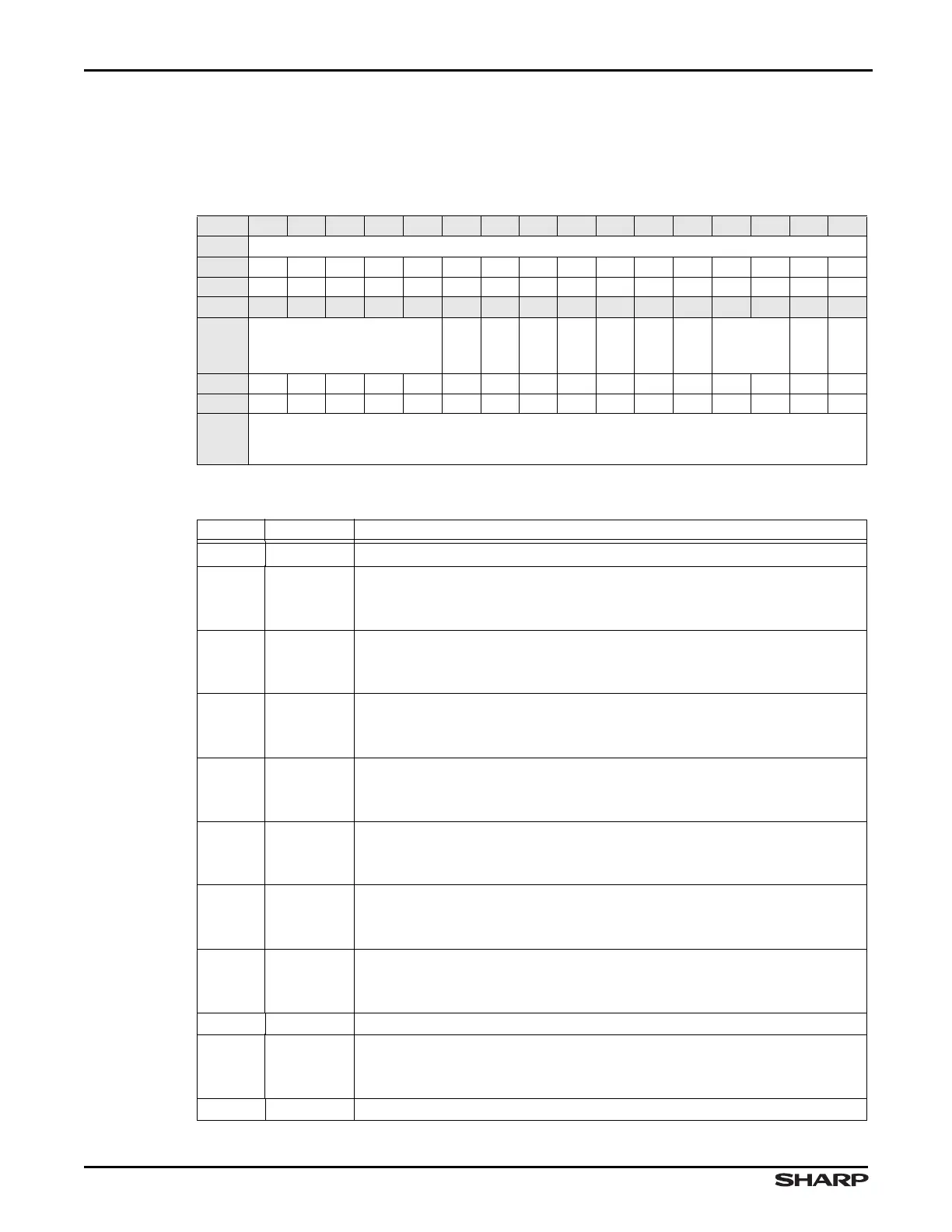

Table 16-32. UARTICR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

OEIC

BEIC

PEARIC

FEIC

RTIC

TXIC

RXIC

///

CTS0IC

///

RESET 0000000000000000

RW RO RO RO RO RO WO WO WO WO WO WO WO RO RO WO RO

ADDR

UART 0: 0xFFFC0000 + 0x044

UART 1: 0xFFFC1000 + 0x044

UART 2: 0xFFFC2000 + 0x044

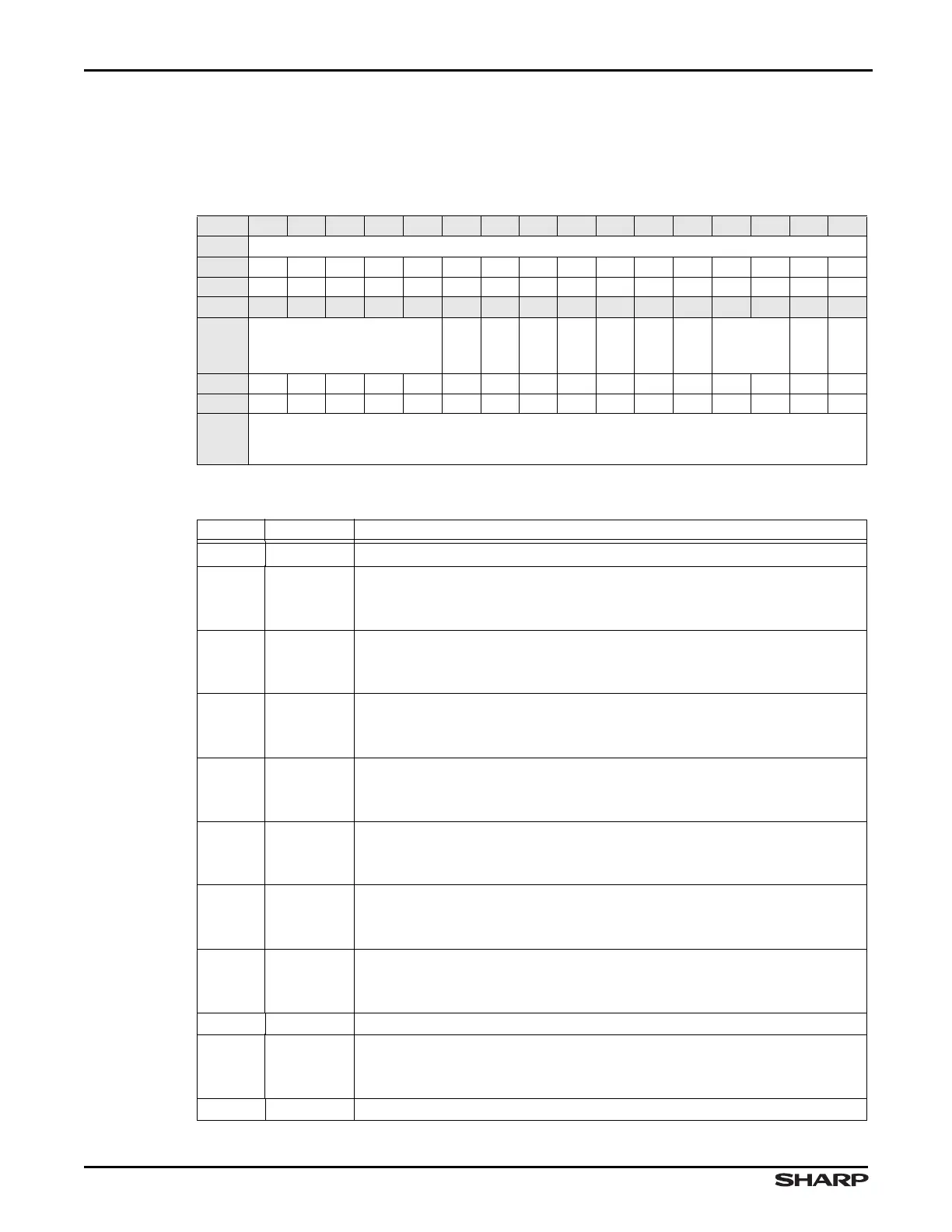

Table 16-33. UARTICR Fields

BIT NAME DESCRIPTION

31:15 /// Reserved Reading returns 0. Write the reset value.

10 OEIC

Overrun Error Interrupt Clear

1 = Clears the interrupt

0 = No effect

9BEIC

Break Error Interrupt Clear

1 = Clears the interrupt

0 = No effect

8 PEARIC

Parity Error/Address Received Interrupt Clear

1 = Clears the interrupt

0 = No effect

7FEIC

Framing Error Interrupt Clear

1 = Clears the interrupt

0 = No effect

6RTIC

Receive Timeout Interrupt Clear

1 = Clears the interrupt

0 = No effect

5TXIC

Transmit Interrupt Clear

1 = Clears the interrupt

0 = No effect

4RXICR

Receive Interrupt Clear

1 = Clears the interrupt

0 = No effect

3:2 /// Reserved Reading returns 0. Write the reset value.

1CTS0IC

CTS0 Interrupt Clear (only for UART0)

1 = Clears the interrupt

0 = No effect

0///Reserved Reading returns 0. Write the reset value.

Loading...

Loading...