LH79524/LH79525 User’s Guide UARTs

Version 1.0 16-17

16.3.2.8 UART Control Register (UARTCR)

UARTCR is the UART Control Register. To enable transmission, bit [8] and bit [0] must be

set. Similarly, to enable reception, bit [9] and bit [0] must be set.

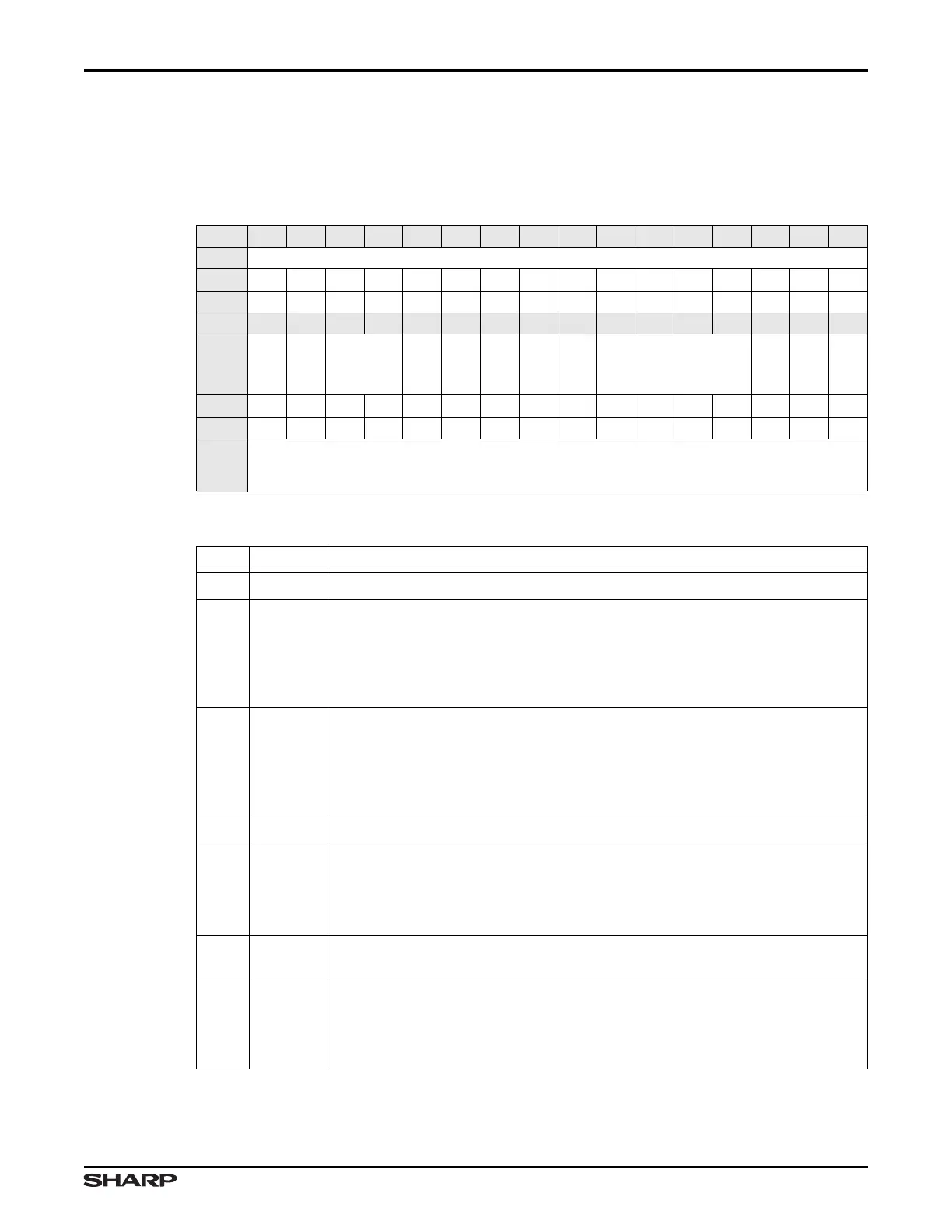

Table 16-22. UARTCR Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD

CTSEN

RTSEN

/// RTS /// RXE TXE LBE ///

SIRLP

SIREN

UARTEN

RESET 0000001100000000

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

ADDR

UART 0: 0xFFFC0000 + 0x030

UART 1: 0xFFFC1000 + 0x030

UART 2: 0xFFFC2000 + 0x030

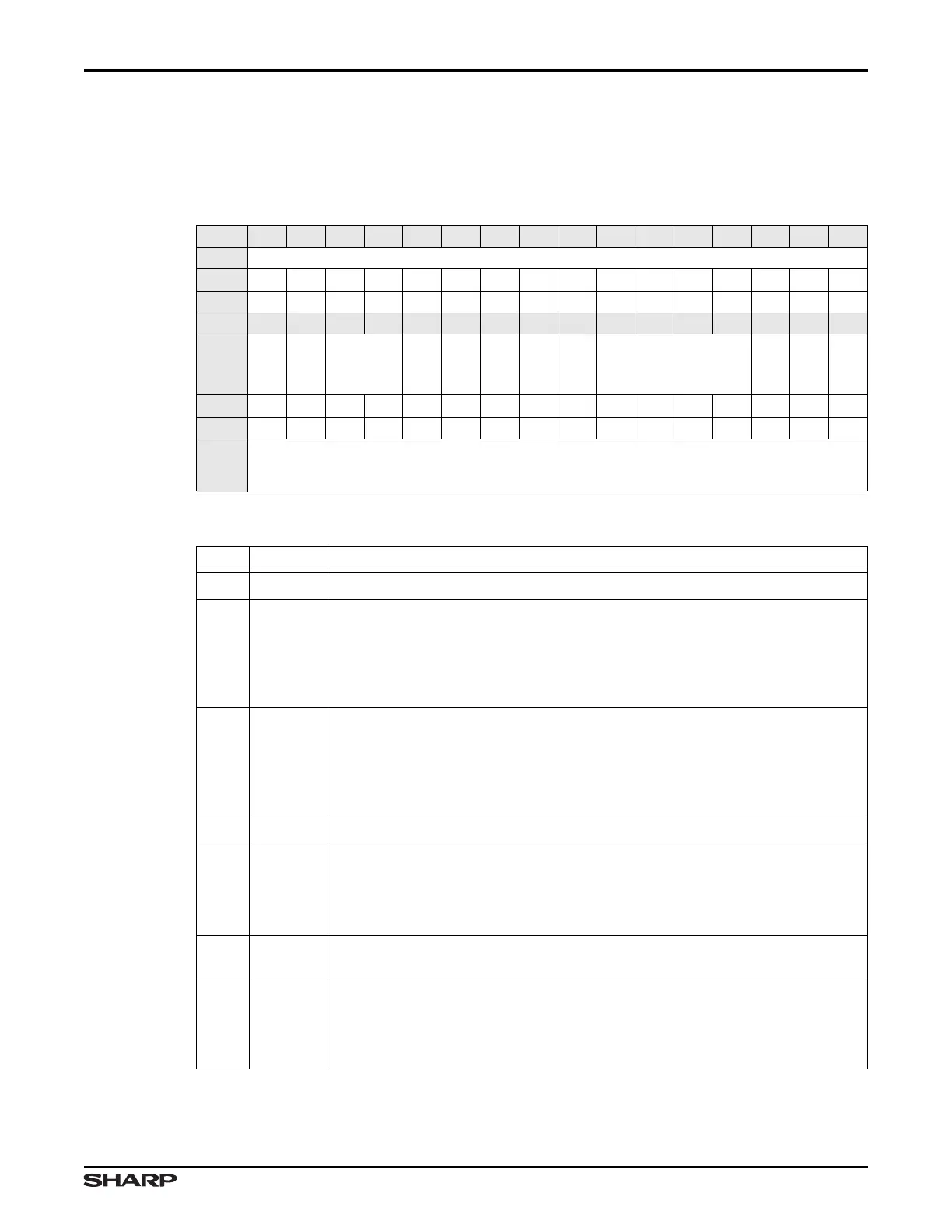

Table 16-23. UARTCR Fields

BIT NAME DESCRIPTION

31:10 /// Reserved Reading returns 0. Write the reset value.

15 CTSEN

CTS Hardware Flow Control Enable (CTSEN) This bit enables CTS hard-

ware flow control. Data is only transmitted when the nUARTCTS signal is as-

serted. (Only used with UART0)

1 = CTS hardware flow control enabled

0 = CTS hardware flow control disabled

14 RTSEN

RTS Hardware Flow Control Enable (RTSEN) This bit enables RTS hard-

ware flow control. Data is only requested when there is space in the receive

FIFO for it to be received. (Only used with UART0)

1 = RTS hardware flow control is enabled

0 = RTS hardware flow control disabled

12:13

/// Reserved Reading returns 0. Write the reset value.

11 RTS

Request to Send (RTS) This bit is the complement of the request to send

(nUARTRTS) modem status output. (Only used with UART0)

1 = The output is 0

0 = The output is 1

10 ///

Reserved Do not modify. When writing to this register, perform a

read-modified-write operation to this bit.

9RXE

Receive Section Enables the receive section of the UART.

1 = Receive section enabled. When the UART is disabled in the middle of

reception, it completes the current character before stopping

0 = Receive section not enabled

Loading...

Loading...