LH79524/LH79525 User’s Guide Reset, Clock, and Power Controller

Version 1.0 13-15

13.2.2.5 Reset Status Register (RSTSTATUS)

This register provides the reset status of the SoC, containing both the external reset status

and the WDT timeout reset status. Following external reset, the EXT bit is 1 and the WDTO

bit is 0. At WDT timeout, only the WDTO bit is 1. The EXT and WDTO bits remain 1 until

they are cleared by writing to the Reset Status Clear register.

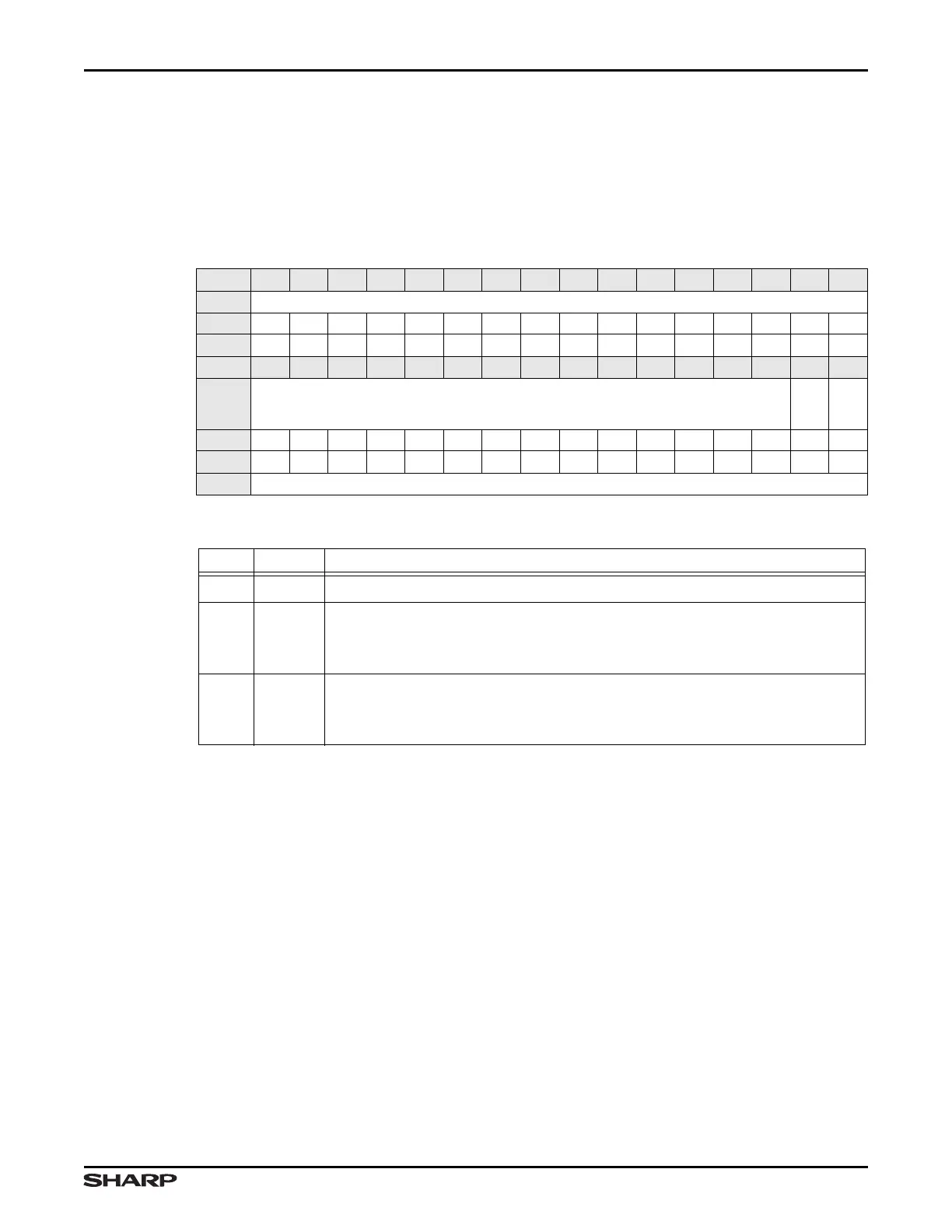

Table 13-12. RSTSTATUS Register

BIT 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FIELD ///

RESET 0000000000000000

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

FIELD ///

WDTO

EXT

RESET 0000000000000001

RW RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO RO

ADDR 0xFFFE2000 + 0x10

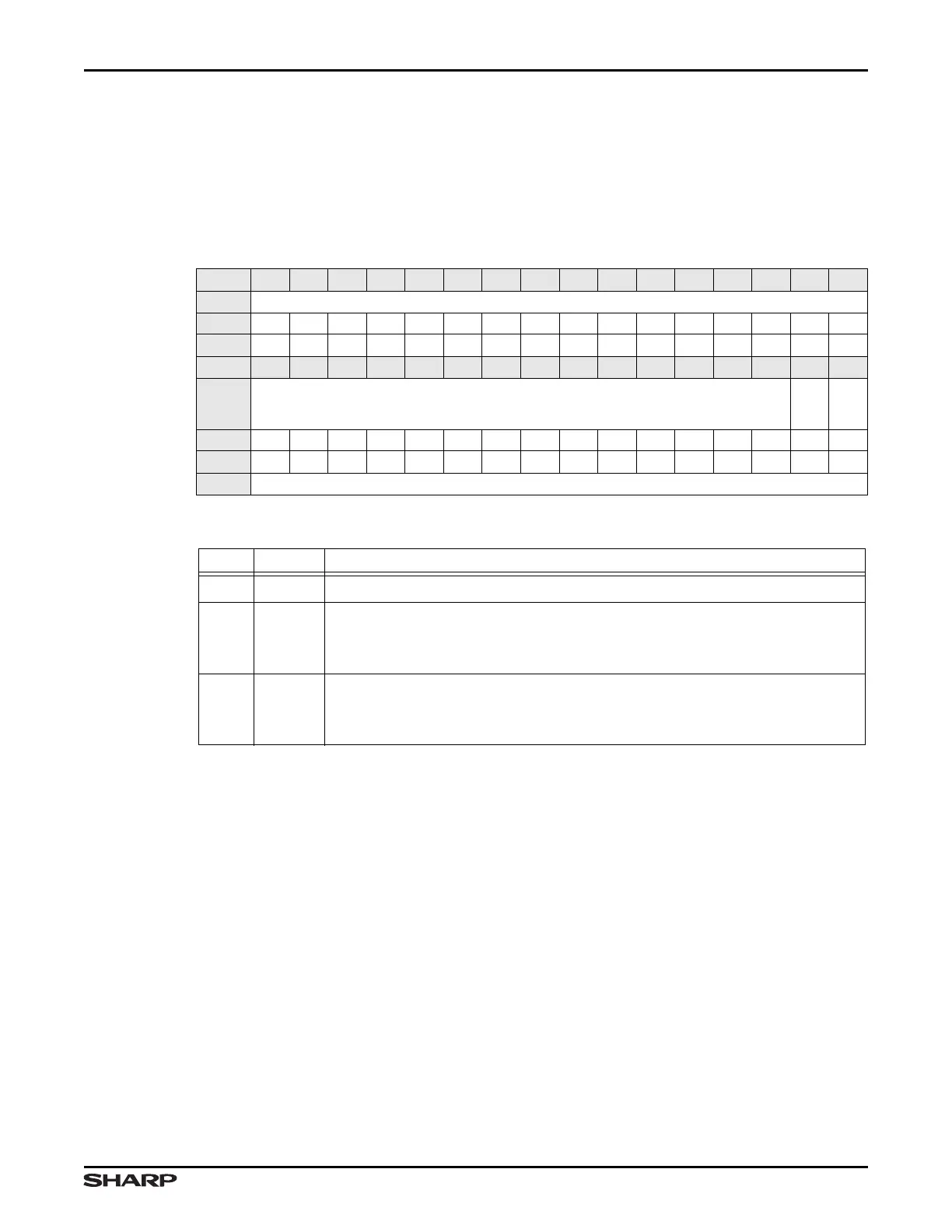

Table 13-13. RSTSTATUS Fields

BITS NAME DESCRIPTION

31:2 /// Reserved Reading returns 0. Write the reset value.

1WDTO

WDT Timeout

1 = WDT timeout has occurred

0 = No WDT timeout has occurred since the flag was last cleared

0 EXT

External Reset

1 = External reset has occurred

0 = No external reset has occurred since the flag was last cleared

Loading...

Loading...