External Memory Controller LH79524/LH79525 User’s Guide

7-24 Version 1.0

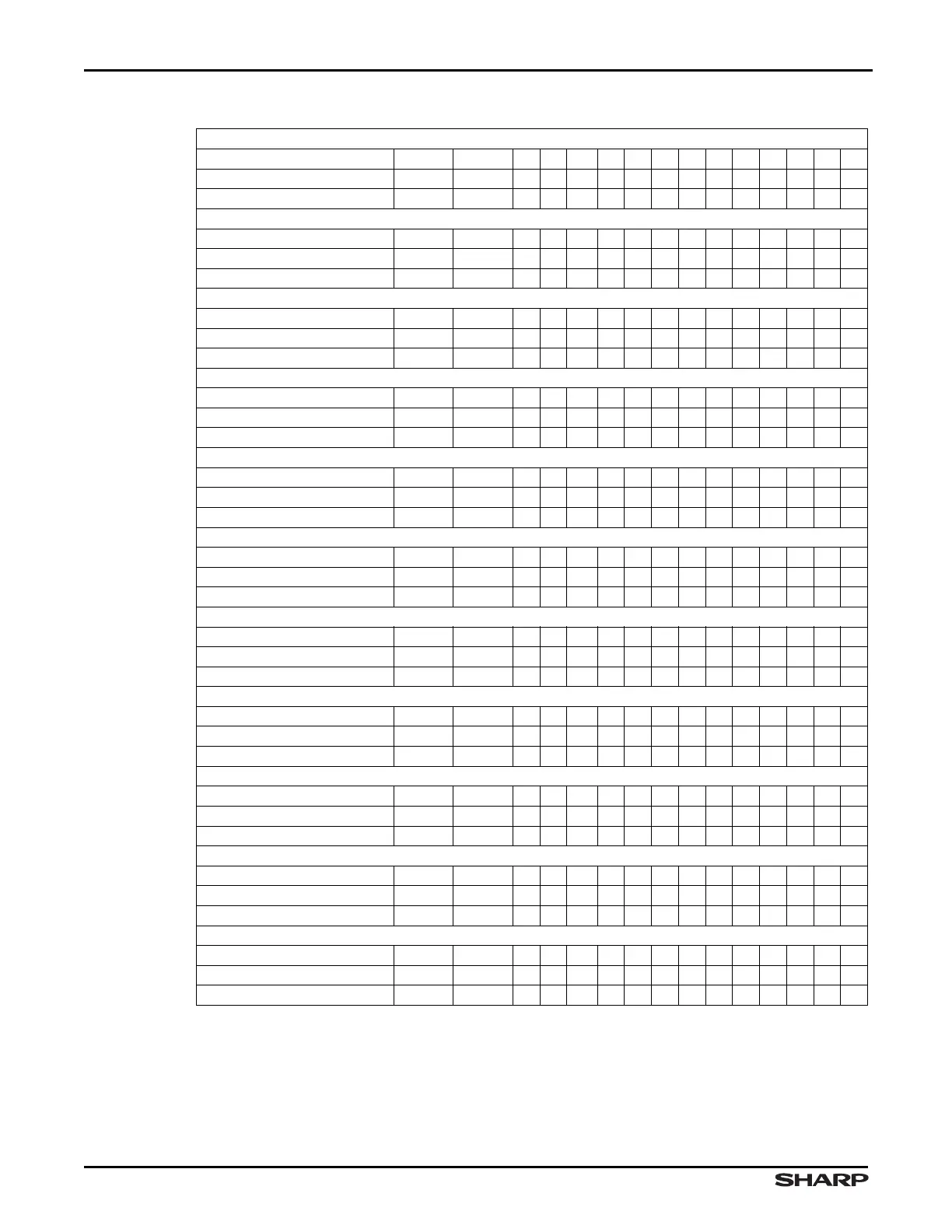

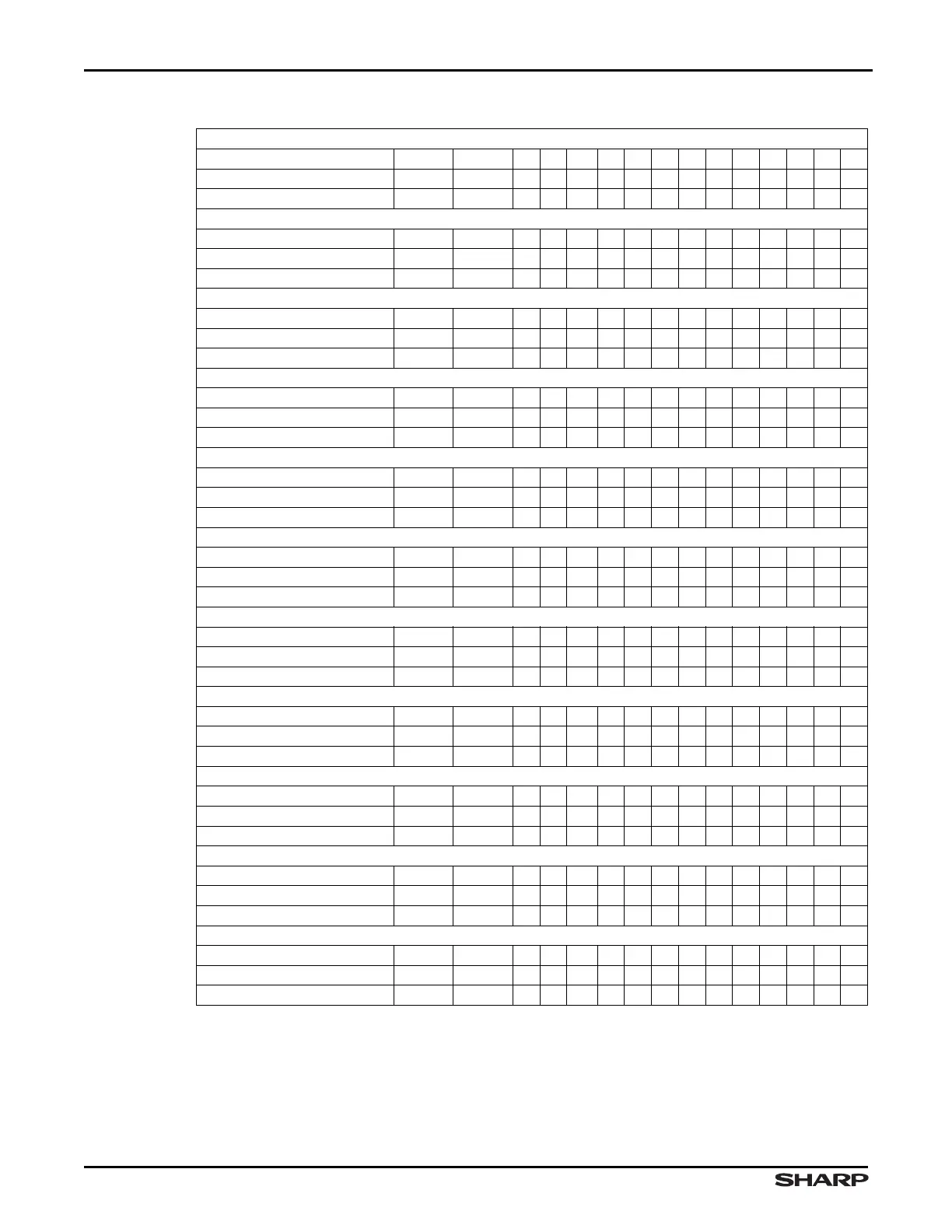

32-BIT DEVICE 64M SDRAM (2M × 32, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 21/BA1 22/BA0 — — 20 19 18 17 16 15 14 13 12 11 10

AHB Address To Column Address 21/BA1 22/BA0 — — AP — — 9 8 7 6 5 4 3 2

32-BIT DEVICE 64M SDRAM (4M × 16, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 23/BA1 22/BA0 — 21 20 19 18 17 16 15 14 13 12 11 10

AHB Address To Column Address 23/BA1 22/BA0 — — AP — — 9 8 7 6 5 4 3 2

32-BIT DEVICE 64M SDRAM (8M × 8, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 23/BA1 24/BA0 — 22 21 20 19 18 17 16 15 14 13 12 11

AHB Address To Column Address 23/BA1 24/BA0 — — AP — 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 128M SDRAM (4M × 32, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 23/BA1 22/BA0 — 21 20 19 18 17 16 15 14 13 12 11 10

AHB Address To Column Address 23/BA1 22/BA0 — — AP — — 9 8 7 6 5 4 3 2

32-BIT DEVICE 128M SDRAM (8M × 16, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 23/BA1 24/BA0 — 22 21 20 19 18 17 16 15 14 13 12 11

AHB Address To Column Address 23/BA1 24/BA0 — — AP — 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 128M SDRAM (16M × 8, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 25/BA1 24/BA0 — 23 22 21 20 19 18 17 16 15 14 13 12

AHB Address To Column Address 25/BA1 24/BA0 — — AP 11 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 256M SDRAM 8M × 32, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 23/BA1 24/BA0 22 21 20 19 18 17 16 15 14 13 12 11 10

AHB Address To Column Address 23/BA1 24/BA0 — — AP — — 9 8 7 6 5 4 3 2

32-BIT DEVICE 256M SDRAM (16M × 16, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 25/BA1 24/BA0 23 22 21 20 19 18 17 16 15 14 13 12 11

AHB Address To Column Address 25/BA1 24/BA0 — — AP — 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 256M SDRAM (32M × 8, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 25/BA1 26/BA0 24 23 22 21 20 19 18 17 16 15 14 13 12

AHB Address To Column Address 25/BA1 26/BA0 — — AP 11 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 512M SDRAM (32M × 16, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 25/BA1 26/BA0 24 23 22 21 20 19 18 17 16 15 14 13 12

AHB Address To Column Address 25/BA1 26/BA0 — — AP 11 10 9 8 7 6 5 4 3 2

32-BIT DEVICE 512M SDRAM (64M × 8, BRC)

External Address Pin, A[14:0] 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AHB Address To Row Address 27/BA1 26/BA0 25 24 23 22 21 20 19 18 17 16 15 14 13

AHB Address To Column Address 27/BA1 26/BA0 — 12 AP 11 10 9 8 7 6 5 4 3 2

Table 7-6. 32-bit Wide Data Bus Address Mapping, SDRAM (BRC) (Cont’d)

Loading...

Loading...