External Memory Controller LH79524/LH79525 User’s Guide

7-50 Version 1.0

NOTES:

1. A Chip Select can be connected to a single memory device, in this case the Chip Select data bus width is

the same as the device width. Alternatively the Chip Select can be connected to a number of external

devices. In this case the Chip Select data bus width is the sum of the memory device data bus widths. For

example, for a Chip Select connected to:

– a 32-bit wide memory device, choose a 32-bit wide address mapping.

– a 16-bit wide memory device, choose a 16-bit wide address mapping.

– four x 8-bit wide memory devices, choose a 32-bit wide address mapping.

– two x 8-bit wide memory devices, choose a 16-bit wide address mapping.

2. The SDRAM column and row width and number of banks are computed automatically from the

address mapping.

3. The SDRAM section of the memory controller does a constant burst of 8 when configured to access 16 bit

memory devices. Similarly, it does burst of 4 when configured to access 32-bit memory devices.

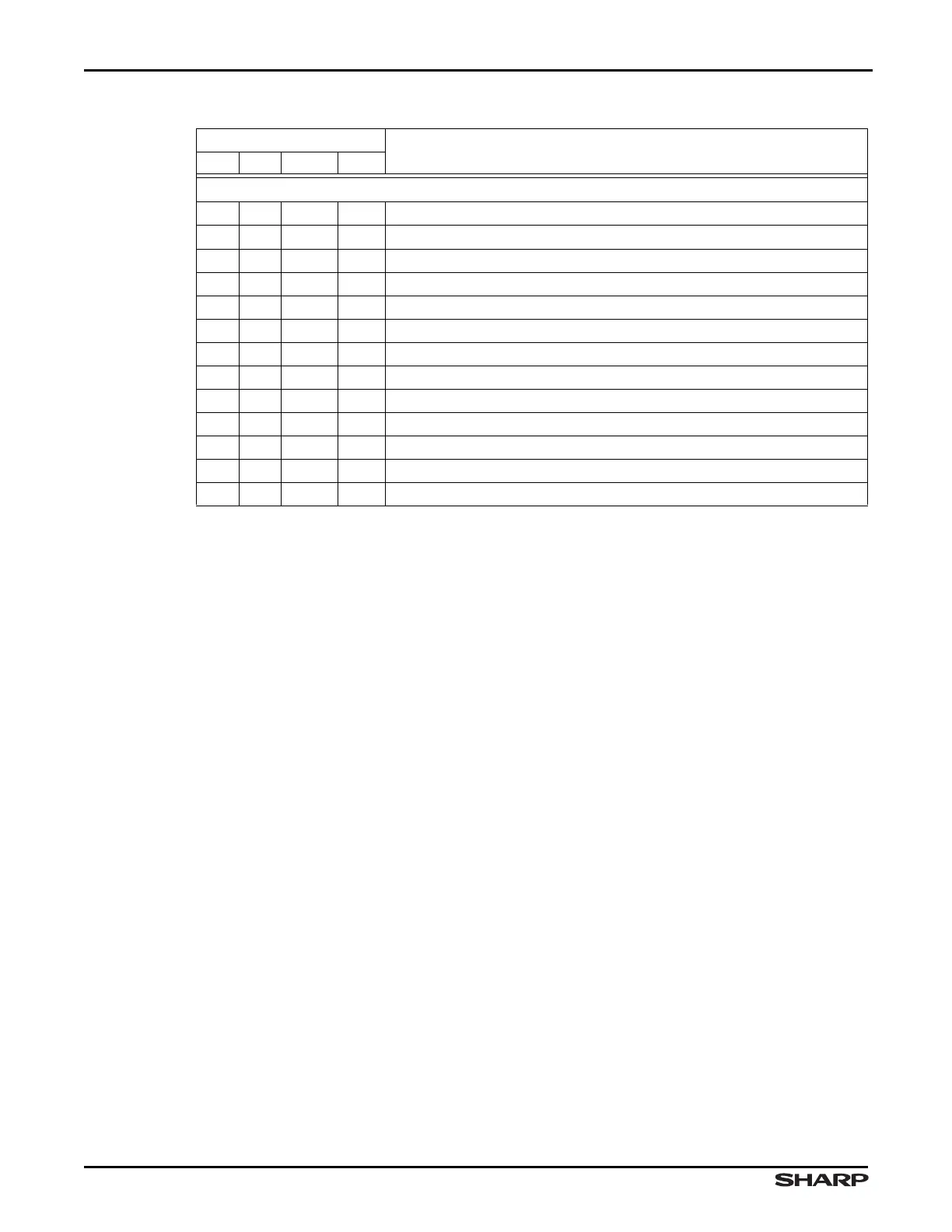

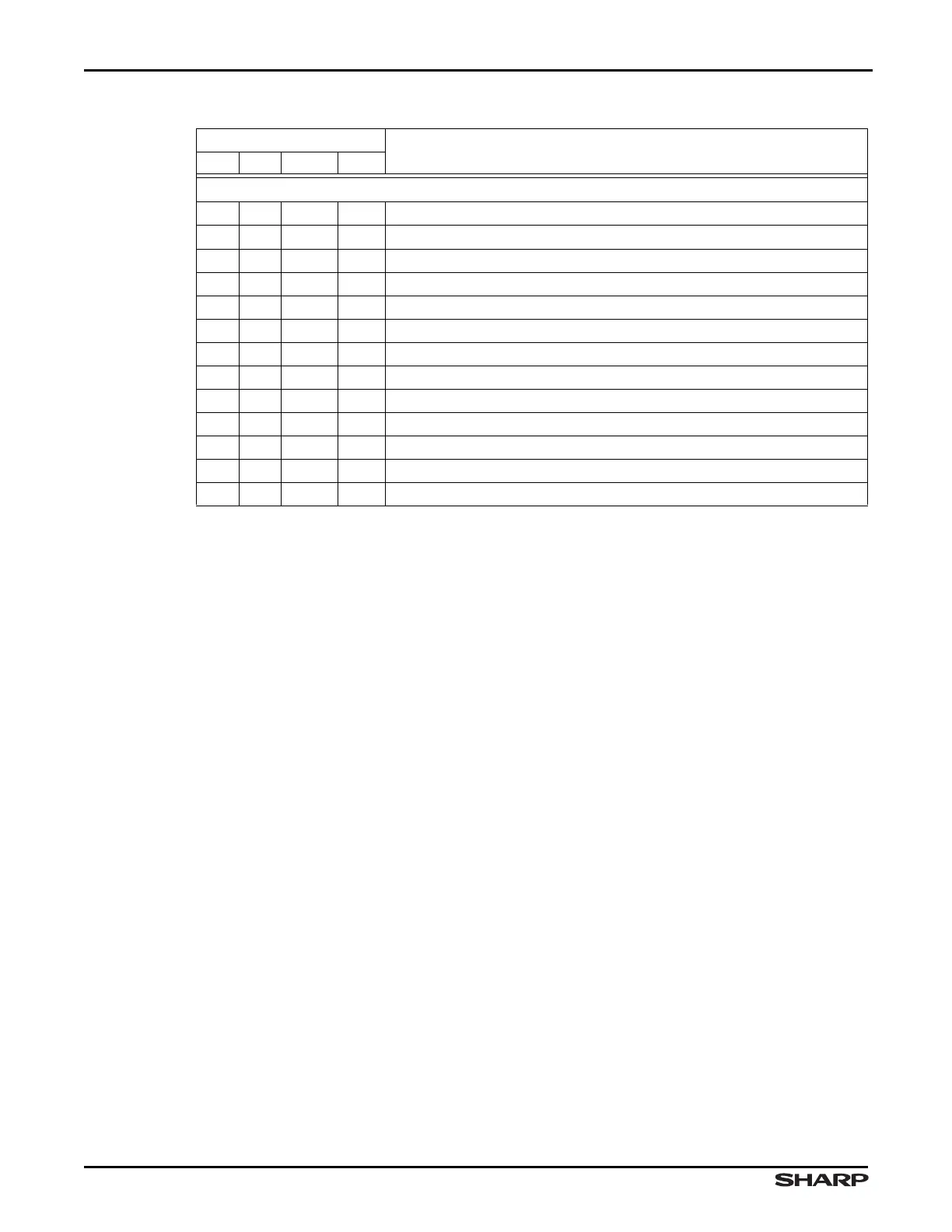

32-BIT EXTERNAL BUS LOW POWER SDRAM ADDRESS MAPPING (ROW, BANK, COLUMN)

1 1 000 00 16Mb (2M × 8), 2 banks, row length = 11, column length = 9

1 1 000 01 16Mb (1M × 16), 2 banks, row length = 11, column length = 8

1 1 001 00 64Mb (8M × 8), 4 banks, row length = 12, column length = 9

1 1 001 01 64Mb (4M × 16), 4 banks, row length = 12, column length = 8

1 1 001 10 64Mb (4M × 16), 4 banks, row length = 11, column length = 8

1 1 010 00 128Mb (16M × 8), 4 banks, row length = 12, column length = 10

1 1 010 01 128Mb (8M × 16), 4 banks, row length = 12, column length = 9

1 1 010 10 128Mb (8M × 16), 4 banks, row length = 12, column length = 8

1 1 011 00 256Mb (32M × 8), 4 banks, row length = 13, column length = 10

1 1 011 01 256Mb (16M × 16), 4 banks, row length = 13, column length = 9

1 1 011 10 256Mb (16M × 16), 4 banks, row length = 13, column length = 8

1 1 100 00 512Mb (64M × 8), 4 banks, row length = 13, column length = 11

1 1 100 01 512Mb (32M × 16), 4 banks, row length = 13, column length = 10

Table 7-49. Address Mapping (Cont’d)

DYNCFGx BITS

DESCRIPTION

[14] [12] [11:9] [8:7]

Loading...

Loading...