Universal Serial Bus Device LH79524/LH79525 User’s Guide

17-28 Version 1.0

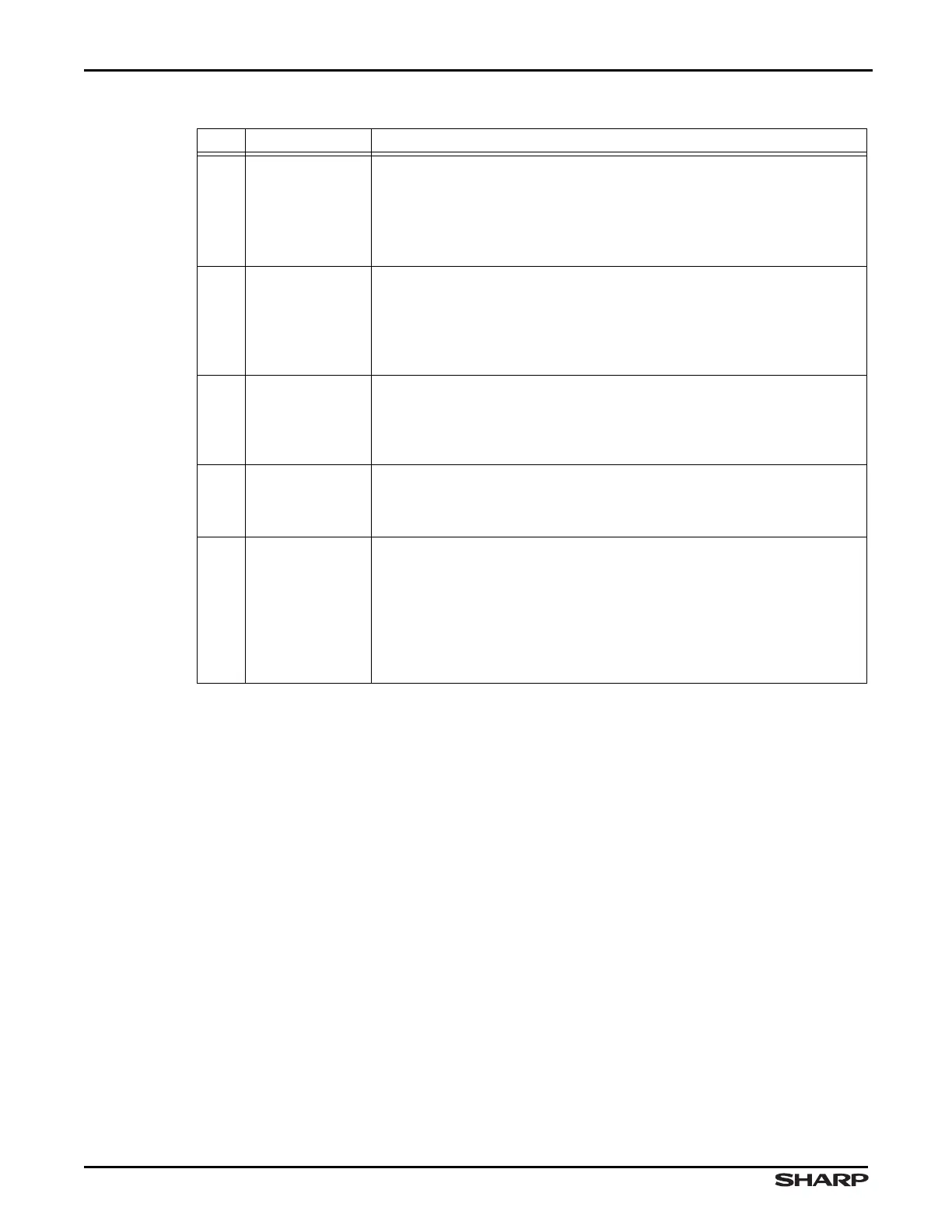

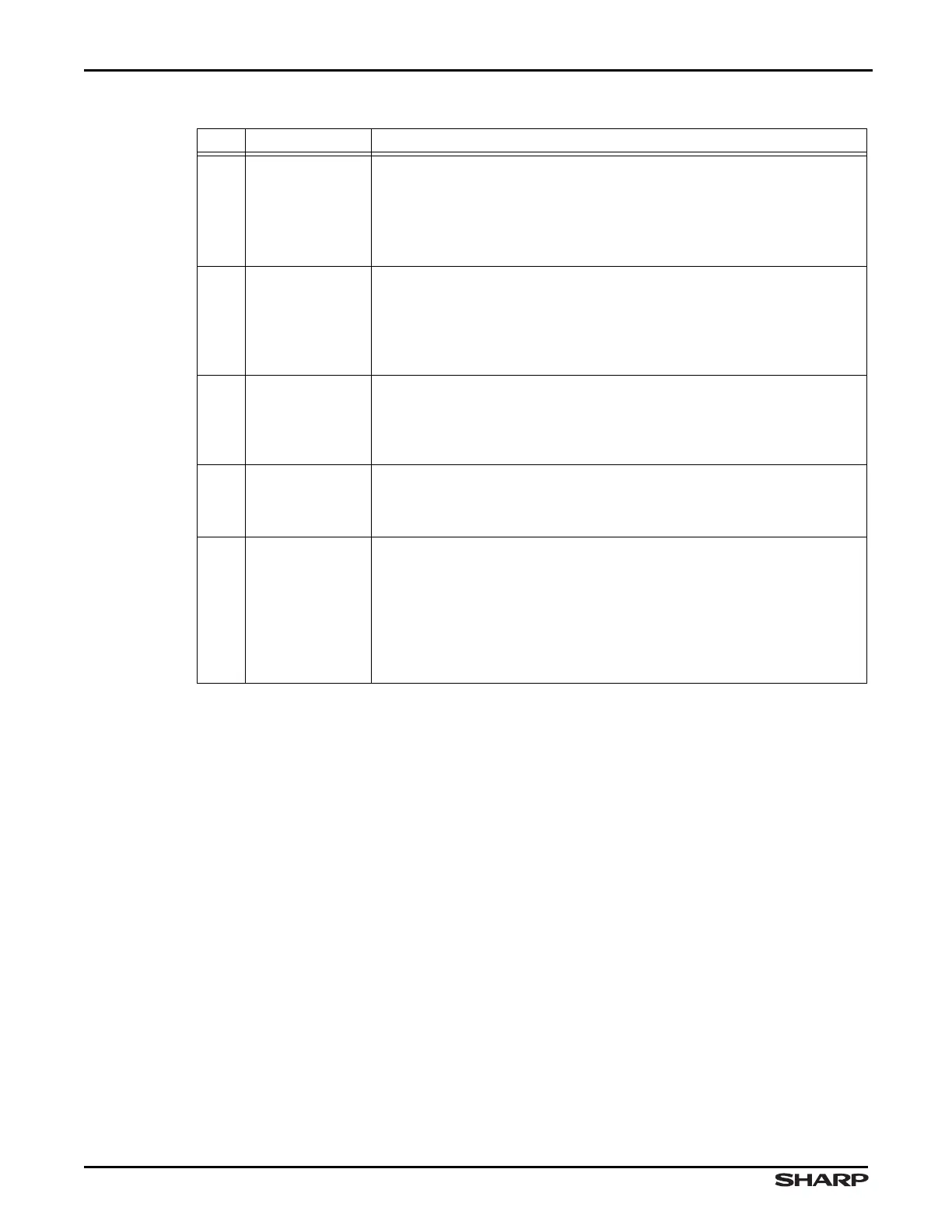

4

FIFO_FLUSH

Flush OUT FIFO Software programs this bit to 1 to flush the FIFO.

This bit can be programmed to 1 only when OUT_PKT_RDY is 1. The

packet due to be unloaded by software will be flushed.

1 = Flush OUT FIFO

0 = Do not flush FIFO

3 DATAERROR

Data Error This bit indicates when OUT_PKT_RDY is set if the data

packet has a CRC or bit-stuff error. This bit is automatically cleared when

OUT_PKT_RDY is cleared. The bit is only valid in isochronous mode.

1 = OUT_PKT_RDY is set and the data packet has a CRC or bit-stuff error

0 = No error

2 OVERRUN

Data Overrun This bit indicates that an OUT packet cannot be loaded

into the OUT FIFO. The bit is only valid in isochronous mode.

1 = An OUT packet cannot be loaded into the OUT FIFO

0 = No error

1

FIFO_FULL

FIFO FULL This bit indicates no more packets can be accepted.

1 = 2 packets are in the IN FIFO, so the FIFO is full

0 = FIFO is not full

0OUT_PKT_RDY

OUT Packet Ready The USB block programs this bit to 1 once the

USB Host has loaded a packet of data into the OUT FIFO. After soft-

ware reads the entire packet from FIFO this bit must be programmed to

0 by software. An interrupt is generated when this bit is set, notifying the

core that a packet is ready to read.

1 = Data packet ready in OUT FIFO

0 = No packet is ready in the OUT FIFO

Table 17-37. OUTCSR1 Fields (Cont’d)

BITS NAME FUNCTION

Loading...

Loading...