RM0016 16-bit advanced control timer (TIM1)

Doc ID 14587 Rev 8 197/449

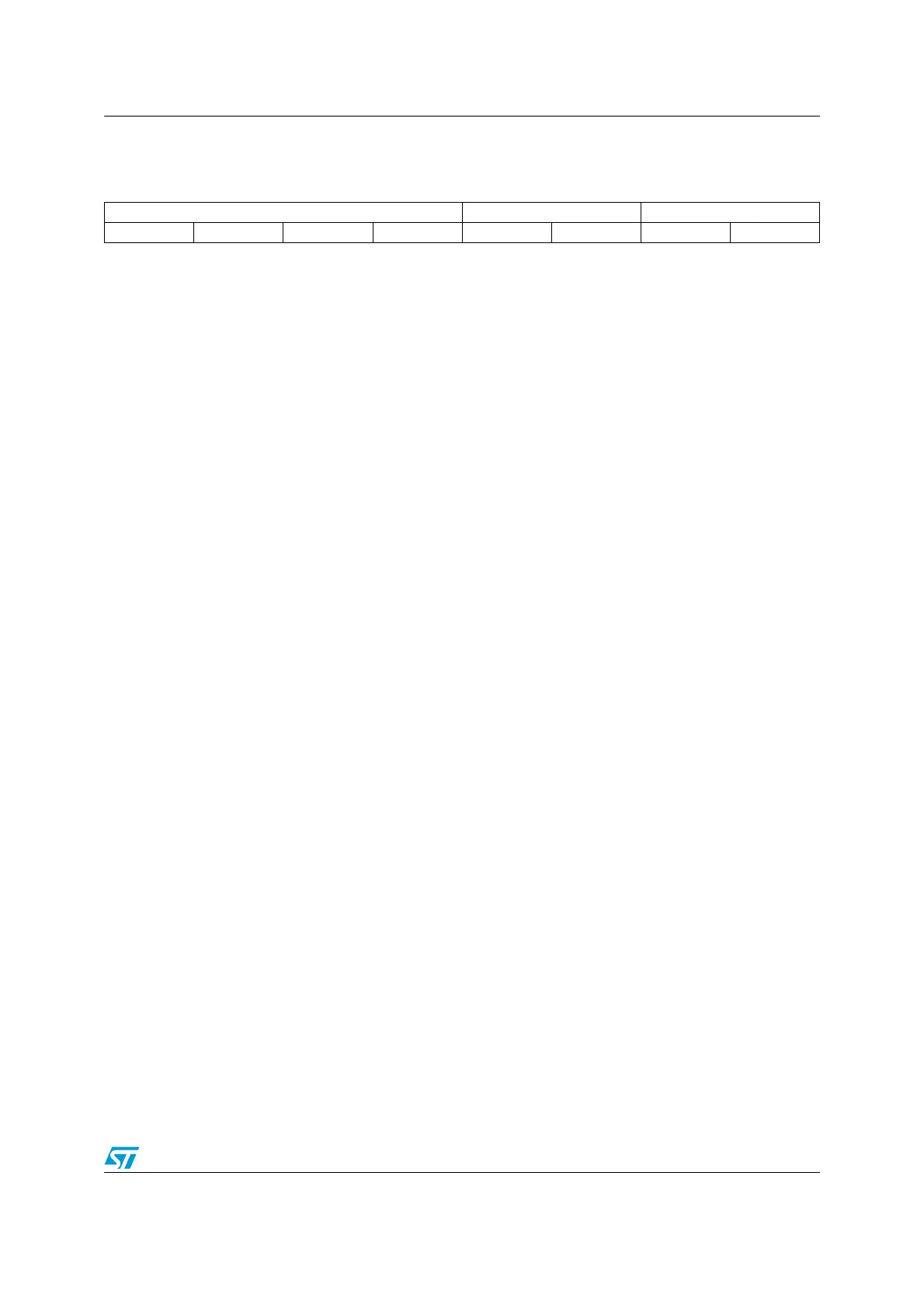

Channel configured in input

76543210

IC1F[3:0] IC1PSC[1:0] CC1S[1:0]

rw rw rw rw rw rw rw rw

Bits 7:4 IC1F[3:0]: Input capture 1 filter

This bitfield defines f

SAMPLING

, the frequency used to sample TI1 input and the length of the digital

filter applied to TI1. The digital filter is made of an event counter in which N events are needed to

validate a transition on the output:

0000: No filter, f

SAMPLING

= f

MASTER

0001: f

SAMPLING

=f

MASTER

, N = 2

0010: f

SAMPLING

=f

MASTER

, N = 4

0011: f

SAMPLING

=f

MASTER

, N = 8

0100: f

SAMPLING

=f

MASTER

/2, N = 6

0101: f

SAMPLING

=f

MASTER

/2, N = 8

0110: f

SAMPLING

=f

MASTER

/4, N = 6

0111: f

SAMPLING

=f

MASTER

/4, N = 8

1000: f

SAMPLING

=f

MASTER

/8, N = 6

1001: f

SAMPLING

=f

MASTER

/8, N = 8

1010: f

SAMPLING

=f

MASTER

/16, N = 5

1011: f

SAMPLING

=f

MASTER

/16, N = 6

1100: f

SAMPLING

=f

MASTER

/16, N = 8

1101: f

SAMPLING

=f

MASTER

/32, N = 5

1110: f

SAMPLING

=f

MASTER

/32, N = 6

1111: f

SAMPLING

=f

MASTER

/32, N = 8

Note: Even on channels that have a complementary output, this bit field is not preloaded and does

not take into account the content of the CCPC bit (in the TIM1_CR2 register).

Bits 3:2 IC1PSC[1:0]: Input capture 1 prescaler

This bitfield defines the ratio of the prescaler acting on CC1 input (IC1). The prescaler is reset as

soon as CC1E = 0 (TIM1_CCER register).

00: No prescaler, capture is made each time an edge is detected on the capture input

01: Capture is made once every 2 events

10: Capture is made once every 4 events

11: Capture is made once every 8 events

Bits 1:0 CC1S[1:0]: Capture/compare 1 selection

This bitfield defines the direction of the channel (input/output) and the used input.

00: CC1 channel is configured as output

01: CC1 channel is configured as input, IC1 is mapped on TI1FP1

10: CC1 channel is configured as input, IC1 is mapped on TI2FP1

11: CC1 channel is configured as input, IC1 is mapped on TRC. This mode works only if an internal

trigger input is selected through the TS bit (TIM1_SMCR register).

Note: CC1S bits are writable only when the channel is OFF (CC1E = 0 in TIM1_CCER1).

Loading...

Loading...